IR3094PBF 데이터 시트보기 (PDF) - International Rectifier

부품명

상세내역

제조사

IR3094PBF Datasheet PDF : 29 Pages

| |||

IR3094PBF

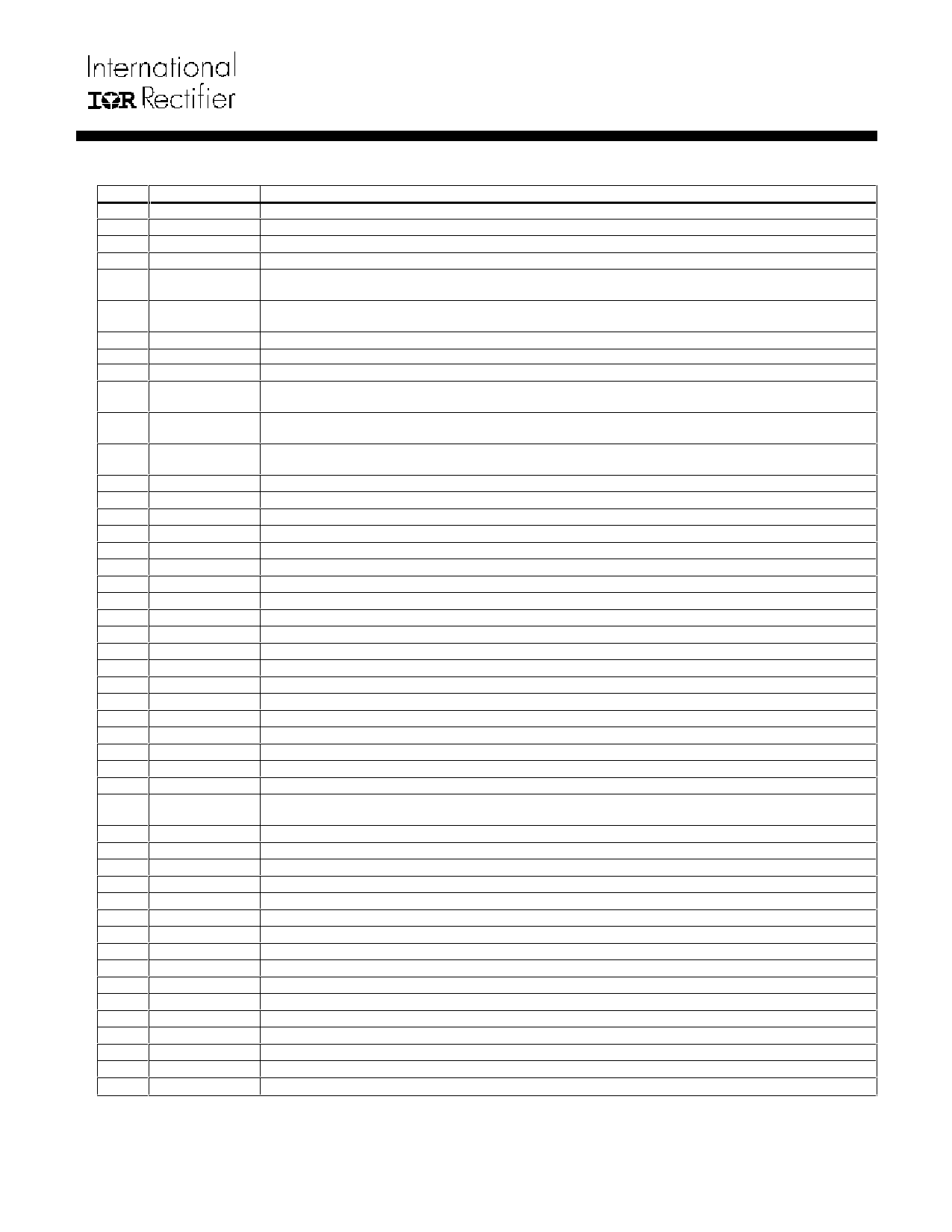

PIN DESCRIPTION

PIN#

1

2

3

4

5

PIN SYMBOL

NC

NC

ROSC

VOSNS-

OCSET

6

VREF

7

VDRP

8

FB

9

EAOUT

10

SS/DEL

11

SCOMP2

12

SCOMP3

13

LGND

14

SETBIAS

15

VCC

16

CSINP3

17

CSINM3

18

BIASOUT

19

PWRGD

20

CSINP2

21

CSINM2

22

NC

23

VCCL3

24

GATEL3

25

PGND3

26

GATEH3

27

VCCH3

28

VCCH2

29

GATEH2

30

PGND2

31

GATEL2

32

5VUVL

33

VCCL1_2

34

GATEL1

35

PGND1

36

GATEH1

37

VCCH1

38

NC

39

CSINM1

40

CSINP1

41

OVP

42

ENABLE

43

OVPSNS

44

5VREF

45

NC

46

NC

47

NC

48

NC

PIN DESCRIPTION

Not connected

Not connected

Connect a resistor to VOSNS- to program oscillator frequency, OCSET and STBIAS bias currents.

Remote Sense Input. Connect to ground at the load.

Programs the hiccup over-current threshold through an external resistor tied to VREF and an internal current

source. The bias current is a function of ROSC.

0.85V Reference voltage. Current Sensing and Over Current Protection are referenced to this pin. An

external RC network tied to VOSNS- is needed for the compensation.

Buffered average current information. Connect an external resistor to FB to program converter output.

.Iinmvepretdinagncineput to the Error Amplifier.

Output of the Error Amplifier.

Controls Converter Softstart, Power Good, and Over-Current Timing. Connect an external capacitor to

LGND to program the timing.

Compensation for the Current Share control loop. Connect a capacitor to ground to set the control loop’s

bandwidth. Phase 2 is forced to match phase 1’s current.

Compensation for the Current Share control loop. Connect a capacitor to ground to set the control loop’s

bandwidth. Phase 3 is forced to match phase 1’s current.

Local Ground and IC substrate connection.

External resistor to ground sets voltage at BIASOUT pin. Bias current is a function of ROSC.

Power for internal circuitry and source for BIASOUT regulator.

Non-inverting input to the Phase 3 Current Sense Amplifier.

Inverting input to the Phase 3 Current Sense Amplifier.

150mA open-looped regulated voltage set by SETBIAS for GATE drive bias.

Open Collector output that drives low during Softstart or any fault condition. Connect external pull-up.

Non-inverting input to the Phase 2 Current Sense Amplifier.

Inverting input to the Phase 2 Current Sense Amplifier.

Not connected

Power for Phase 3 Low-Side Gate Driver.

Phase 3 Low-Side Gate Driver Output and input to GATEH3 non-overlap comparator.

Return for Phase 3 Gate Drivers.

Phase 3 High-Side Gate Driver Output and input to GATEL3 non-overlap comparator.

Power for Phase 3 High-Side Gate Driver.

Power for Phase 2 High-Side Gate Driver.

Phase 2 High-Side Gate Driver Output and input to GATEL2 non-overlap comparator.

Return for Phase 2 Gate Drivers.

Phase 2 Low-Side Gate Driver Output and input to GATEH2 non-overlap comparator.

Can be used to monitor the driver supply voltage or 5V supply voltage when converting from 5V. An under

voltage condition initiates Soft Start.

Power for Phase 1 and 2 Low-Side Gate Drivers.

Phase 1 Low-Side Gate Driver Output and input to GATEH1 non-overlap comparator.

Return for Phase 1 Gate Drivers.

Phase 1 High-Side Gate Driver Output and input to GATEL1 non-overlap comparator.

Power for Phase 1 High-Side Gate Driver.

Not connected

Inverting input to the Phase 1 Current Sense Amplifier.

Non-inverting input to the Current Sense Amplifier.

Output that drives high during an Over-Voltage condition.

Enable Input. A logic low applied to this pin puts the IC into Fault mode.

Dedicated output voltage sense pin for Over Voltage Protection.

Decoupling for internal voltage reference rail.

Not connected

Not connected

Not connected

Not connected

Page 2 of 29

09/26/05