1357 데이터 시트보기 (PDF) - Linear Technology

부품명

상세내역

제조사

1357 Datasheet PDF : 12 Pages

| |||

LT1357

APPLICATIONS INFORMATION

has no effect under normal operation. When driving a

capacitive load (or a low value resistive load) the network

is incompletely bootstrapped and adds to the compensa-

tion at the high impedance node. The added capacitance

slows down the amplifier which improves the phase

margin by moving the unity-gain frequency away from the

pole formed by the output impedance and the capacitive

load. The zero created by the RC combination adds phase

to ensure that even for very large load capacitances, the

total phase lag can never exceed 180 degrees (zero phase

margin) and the amplifier remains stable.

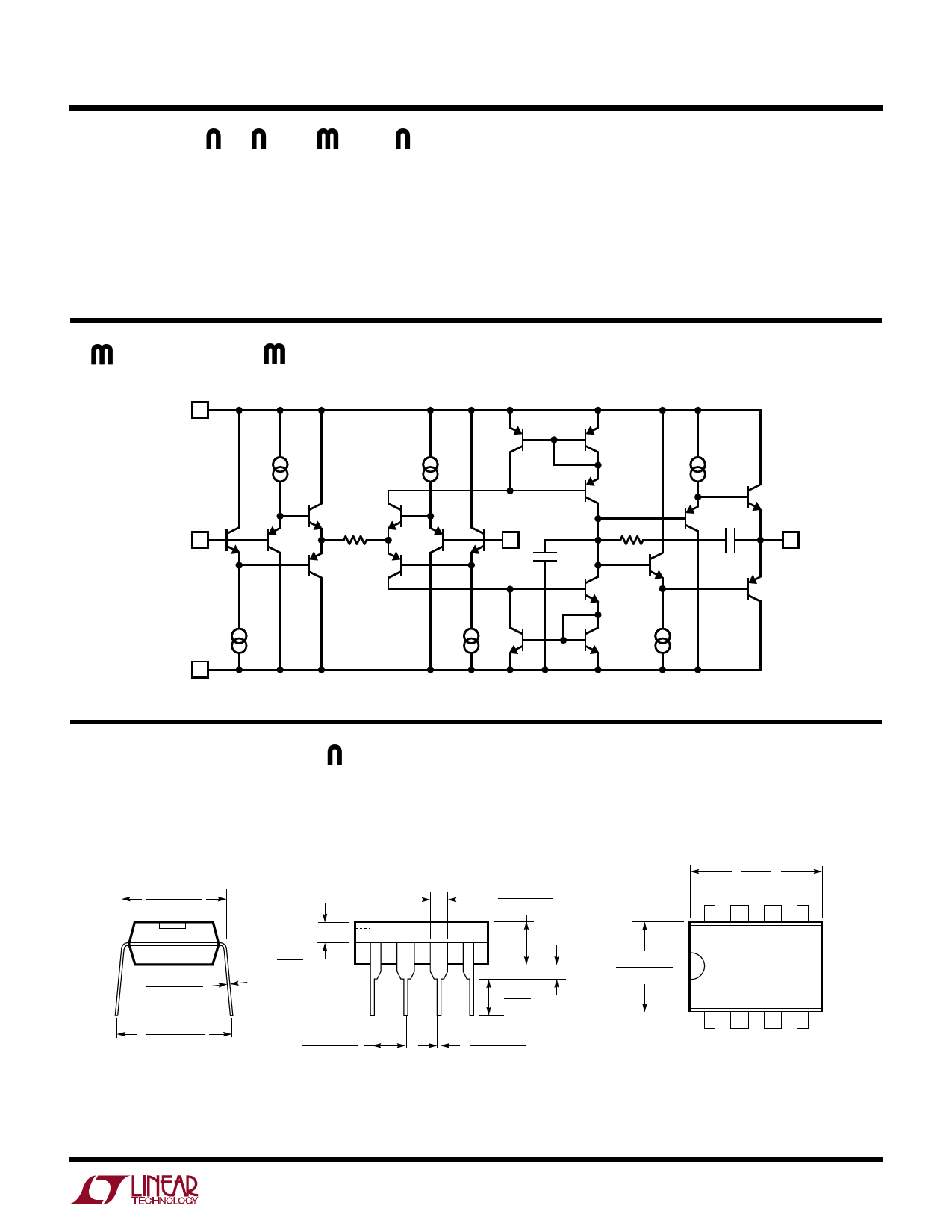

SI PLIFIED SCHE ATIC

V+

R1

500Ω

+IN

RC

–IN

OUT

C

CC

V–

1357 SS01

PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

0.300 – 0.325

(7.620 – 8.255)

N8 Package

8-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

0.045 – 0.065

(1.143 – 1.651)

0.130 ± 0.005

(3.302 ± 0.127)

0.400*

(10.160)

MAX

8

7

6

5

0.009 – 0.015

(0.229 – 0.381)

+0.035

0.325 –0.015

( ) 8.255

+0.889

–0.381

0.065

(1.651)

TYP

0.100 ± 0.010

(2.540 ± 0.254)

*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

0.125

(3.175) 0.020

MIN (0.508)

MIN

0.018 ± 0.003

(0.457 ± 0.076)

0.255 ± 0.015*

(6.477 ± 0.381)

12

34

N8 1197

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-

tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

11