IS61VPD10018-200B 데이터 시트보기 (PDF) - Integrated Silicon Solution

부품명

상세내역

제조사

IS61VPD10018-200B

IS61VPD10018-200B Datasheet PDF : 24 Pages

| |||

IS61VPD51232 IS61VPD51236 IS61VPD10018

ISSI ®

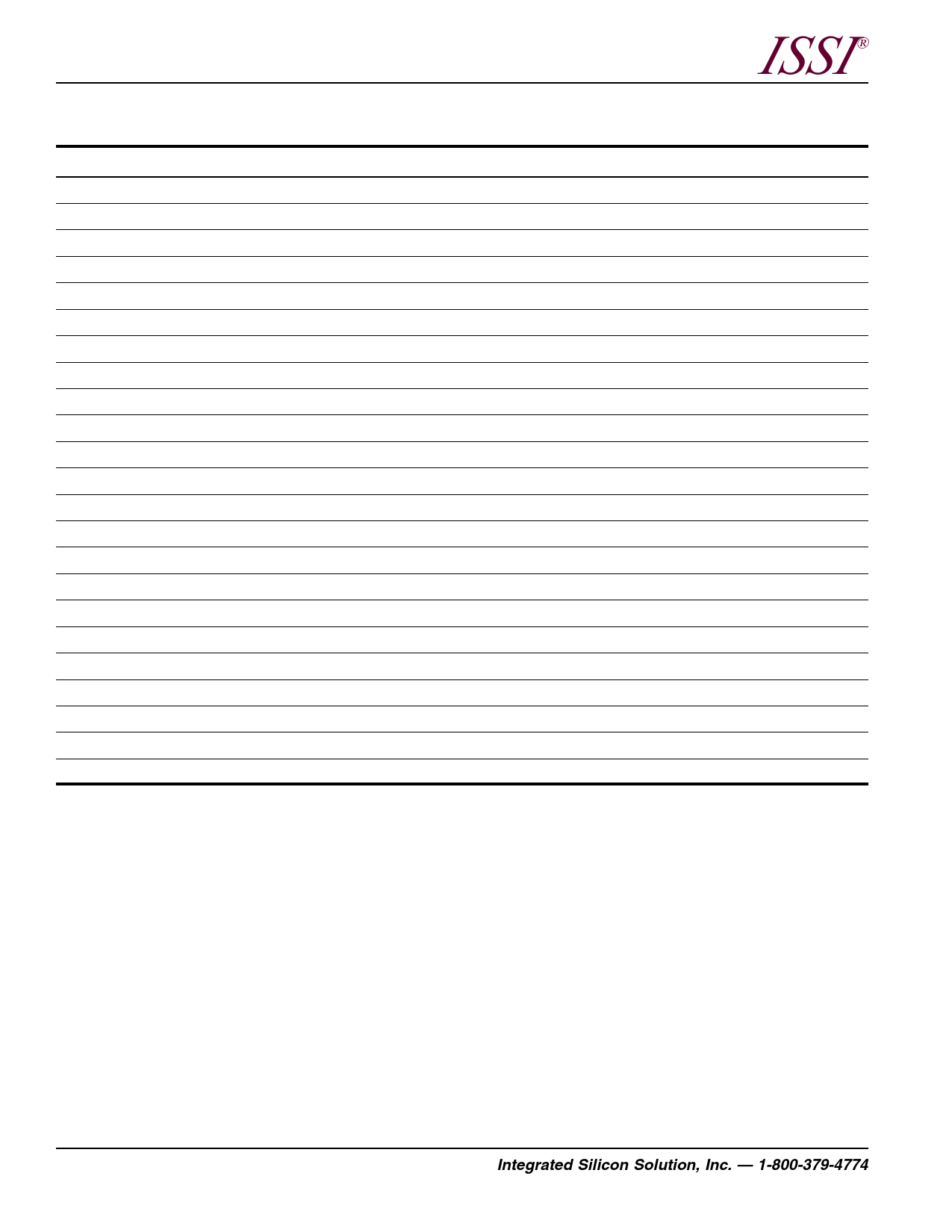

TRUTH TABLE(1-8) (3CE option)

OPERATION

ADDRESS CE CE2 CE2 ZZ ADSP ADSC ADV WRITE OE CLK

DQ

Deselect Cycle, Power-Down

None

H

X

X

L

X

L

X

X

X L-H

High-Z

Deselect Cycle, Power-Down

None

L

X

L

L

L

X

X

X

X L-H

High-Z

Deselect Cycle, Power-Down

None

L

H

X

L

L

X

X

X

X L-H

High-Z

Deselect Cycle, Power-Down

None

L

X

L

L

H

L

X

X

X L-H

High-Z

Deselect Cycle, Power-Down

None

L

H

X

L

H

L

X

X

X L-H

High-Z

Snooze Mode, Power-Down

None X X X H X X X X X X

High-Z

Read Cycle, Begin Burst

External L

L

H

L

L

X

X

X

L L-H

Q

Read Cycle, Begin Burst

External L

L

H

L

L

X

X

X

H L-H

High-Z

Write Cycle, Begin Burst

External L

L

H

L

H

L

X

L

X L-H

D

Read Cycle, Begin Burst

External L

L

H

L

H

L

X

H

L L-H

Q

Read Cycle, Begin Burst

External L

L

H

L

H

L

X

H

H L-H

High-Z

Read Cycle, Continue Burst

Next

X

X

X

L

H

H

L

H

L L-H

Q

Read Cycle, Continue Burst

Next

X

X

X

L

H

H

L

H

H L-H

High-Z

Read Cycle, Continue Burst

Next

H

X

X

L

X

H

L

H

L L-H

Q

Read Cycle, Continue Burst

Next

H

X

X

L

X

H

L

H

H L-H

High-Z

Write Cycle, Continue Burst

Next

X

X

X

L

H

H

L

L

X L-H

D

Write Cycle, Continue Burst

Next

H

X

X

L

X

H

L

L

X L-H

D

Read Cycle, Suspend Burst

Current X

X

X

L

H

H

H

H

L L-H

Q

Read Cycle, Suspend Burst

Current X

X

X

L

H

H

H

H

H L-H

High-Z

Read Cycle, Suspend Burst

Current H

X

X

L

X

H

H

H

L L-H

Q

Read Cycle, Suspend Burst

Current H

X

X

L

X

H

H

H

H L-H

High-Z

Write Cycle, Suspend Burst

Current X

X

X

L

H

H

H

L

X L-H

D

Write Cycle, Suspend Burst

Current H

X

X

L

X

H

H

L

X L-H

D

NOTE:

1. X means “Don’t Care.” H means logic HIGH. L means logic LOW.

2. For WRITE, L means one or more byte write enable signals (BWa, BWb, BWc or BWd) and BWE are LOW or GW is LOW.

WRITE = H for all BWx, BWE, GW HIGH.

3. BWa enables WRITEs to DQa’s and DQPa. BWb enables WRITEs to DQb’s and DQPb. BWc enables WRITEs to DQc’s and

DQPc. BWd enables WRITEs to DQd’s and DQPd. DQPa and DQPb are only available on the x18 and x36 versions. DQPc and

DQPd are only available on the x36 version.

4. All inputs except OE and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

5. Wait states are inserted by suspending burst.

6. For a WRITE operation following a READ operation, OE must be HIGH before the input data setup time and held HIGH during the

input data hold time.

7. This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

8. ADSP LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more byte write

enable signals and BWE LOW or GW LOW for the subsequent L-H edge of CLK. See WRITE timing diagram for clarification.

6

Integrated Silicon Solution, Inc. — 1-800-379-4774

ADVANCE INFORMATION Rev. 00B

09/25/01