MSM6242B 데이터 시트보기 (PDF) - Oki Electric Industry

부품명

상세내역

제조사

MSM6242B Datasheet PDF : 18 Pages

| |||

MSM6242B

¡ Semiconductor

FUNCTIONAL DESCRIPTION OF REGISTERS

S , S , MI , MI , H , H , D , D , MO , MO , Y , Y , W

1 10

1

10 1 10 1 10

1

10 1 10

a) These are abbreviations for SECOND1, SECOND10, MINUTE1, MINUTE10, HOUR1,

HOUR10, DAY1, DAY10, MONTH1, MONTH10, YEAR1, YEAR10, and WEEK. These

values are in BCD notation.

b) All registers are logically positive. For example, (S8, S4, S2, S1) = 1001 which means 9

seconds.

c) If data is written which is out of the clock register data limits, it can result in erroneous clock

data being read back.

d) PM/AM, h20, h10

In the mode setting of 24-hour mode, PM/AM bit is ignored, while in the setting of 12-hour

mode h20 is to be set. Otherwise it causes a discrepancy. In reading out the PM/AM bit in

the 24-hour mode, it is continuously read out as 0. In reading out h20 bit in the 12-hour mode,

0 is written into this bit first, then it is continuously read out as 0 unless 1 is being written

into this bit.

e) Registers Y1, Y10, and Leap Year. The MSM6242B is designed exclusively for the Christian

Era and is capable of identifying a leap year automatically. The result of the setting of a non-

existant day of the month is shown in the following example: If the date February 29 or

November 31, 1985, was written, it would be changed automatically to March 1, or

December 1, 1985 at the exact time at which a carry pulse occurs for the day's digit.

f) The Register W data limits are 0 – 6 (Tabel 1 shows a possible data definition).

w4

w2

0

0

0

0

0

1

0

1

1

0

1

0

1

1

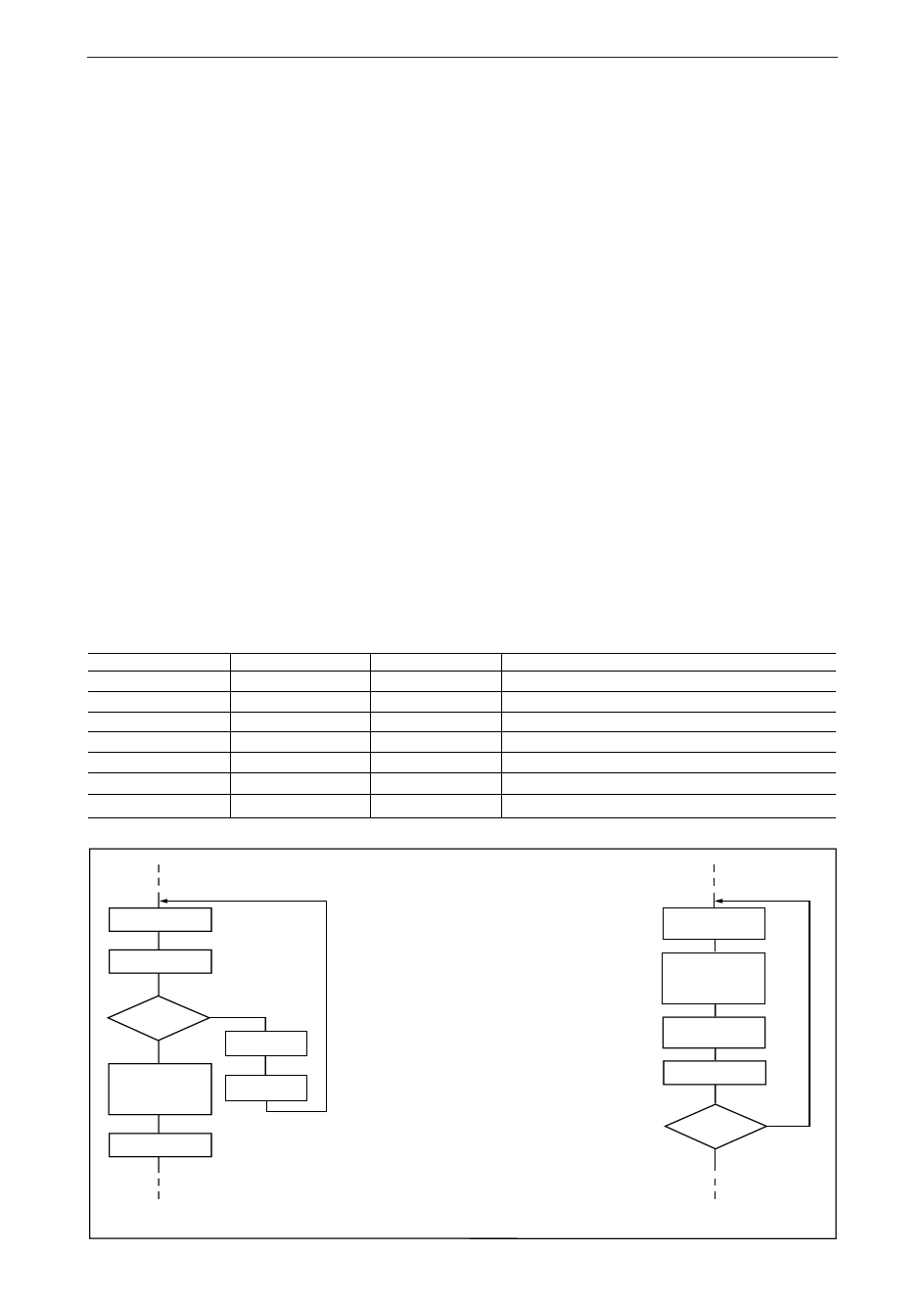

Using HOLD Bit

TABLE 1

w1

0

1

0

1

0

1

0

Day of Week

Sunday

Monday

Tuesday

Wednesday

Thursday

Friday

Saturday

Not Using HOLD Bit

HOLD Bit ← 1

Read BUSY Bit

Busy Bit= O?

YES

Write data into

or Read data from

registers S1 ~ W

NO

HOLD Bit ← 0

Idling Time

HOLD Bit ← 0

*

* In the inside of LSI, the CLEAR of BUSY bit is performed when

HOLD bit = 0, but, if the period of HOLD bit =0 is extermely

narrow as compared with the period of HOLD bit = 1, there is

some case that the CLEAR of BUSY bit delays so that the

BUSY bit can be cleared by sampling HOLD bit = 0 at approximate

16KHz. It is recommended to allow an idling time of 62ms or more.

Read Register

S1 ~ W

First

Data of

DATA ← S1 ~ W

Register

Read Register

S1 ~ W

Second

DATA1 = DATA2

NO

DATA1 = DATA2

YES

Figure 10. Reading and Writing of Registers S1 ~ W

32