M74HC181 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

M74HC181 Datasheet PDF : 15 Pages

| |||

M74HC181

ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR

s HIGH SPEED:

tPD= 13 ns (TYP.) at VCC = 6V

s LOW POWER DISSIPATION:

ICC = 4µA(MAX.) at TA=25°C

s HIGH NOISE IMMUNITY:

VNIH = VNIL = 28 % VCC (MIN.)

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 181

DESCRIPTION

The M74HC181 is an high speed CMOS

ARITHMETIC LOGIC UNIT/FUNCTION

GENERATOR fabricated with silicon gate

C2MOS technology.

This circuit performs 16 binary arithmetic

operations on two 4-bit words as shown in tables 1

and 2. These operations are selected by the four

function select lines (S0, S1, S2, S3) and include

addition, subtraction, decrement and straight

transfer. When performing arithmetic

manipulations, the internal carries must be

enabled by applying a low level voltage to the

mode control input (M). A full carry look-ahead

scheme is made available in these devices for

fast, simultaneous carry generation by means of

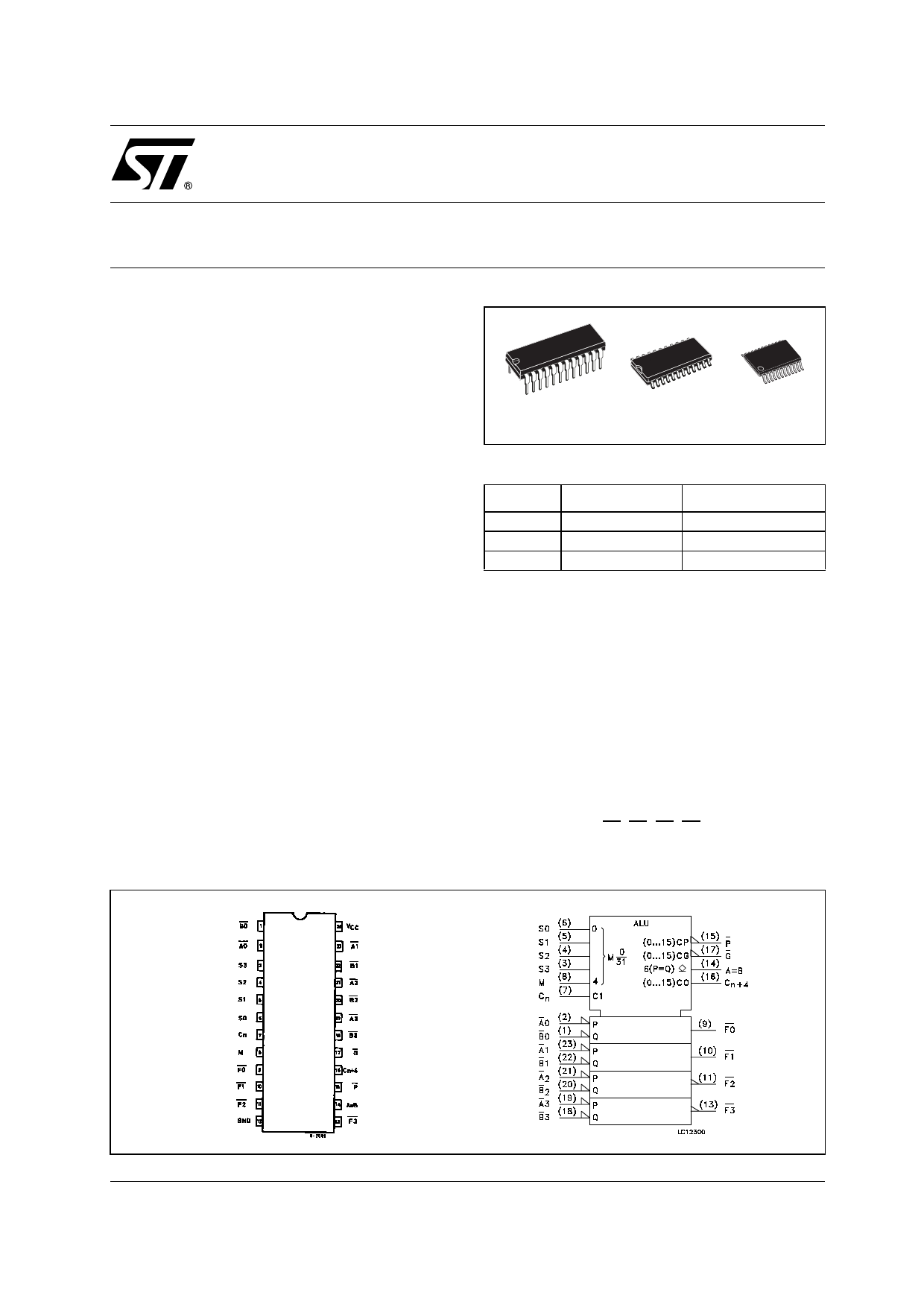

PIN CONNECTION AND IEC LOGIC SYMBOLS

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

TSSOP

M74HC181B1R

M74HC181M1R

T&R

M74HC181RM13TR

M74HC181TTR

two cascade-outputs (pins 15 and 17) for the four

bits in the package. When used in conjunction with

the M74HC182, full carry look-ahead circuits, high

speed arithmetic operations can be performed.

These circuits will accommodate active-high or

active-low data, if the pin designations are

interpreted as shown below . Subtraction is

accomplished by 1,s complement addition where

1’s complement of the subtrahend is generated

internally. The resultant output is 1-B-1, which

requires an end around or forced carry to produce

A-B. The 181 can also be utilized as a comparator.

The A=B output is internally decoded from the

function outputs (F0, F1, F2, F3) so that when two

words of equal magnitude are applied at the A and

April 2003

1/15