MAX6323(2003) 데이터 시트보기 (PDF) - Maxim Integrated

부품명

상세내역

제조사

MAX6323

(Rev.:2003)

(Rev.:2003)

MAX6323 Datasheet PDF : 12 Pages

| |||

µP Supervisory Circuits with Windowed

(Min/Max) Watchdog and Manual Reset

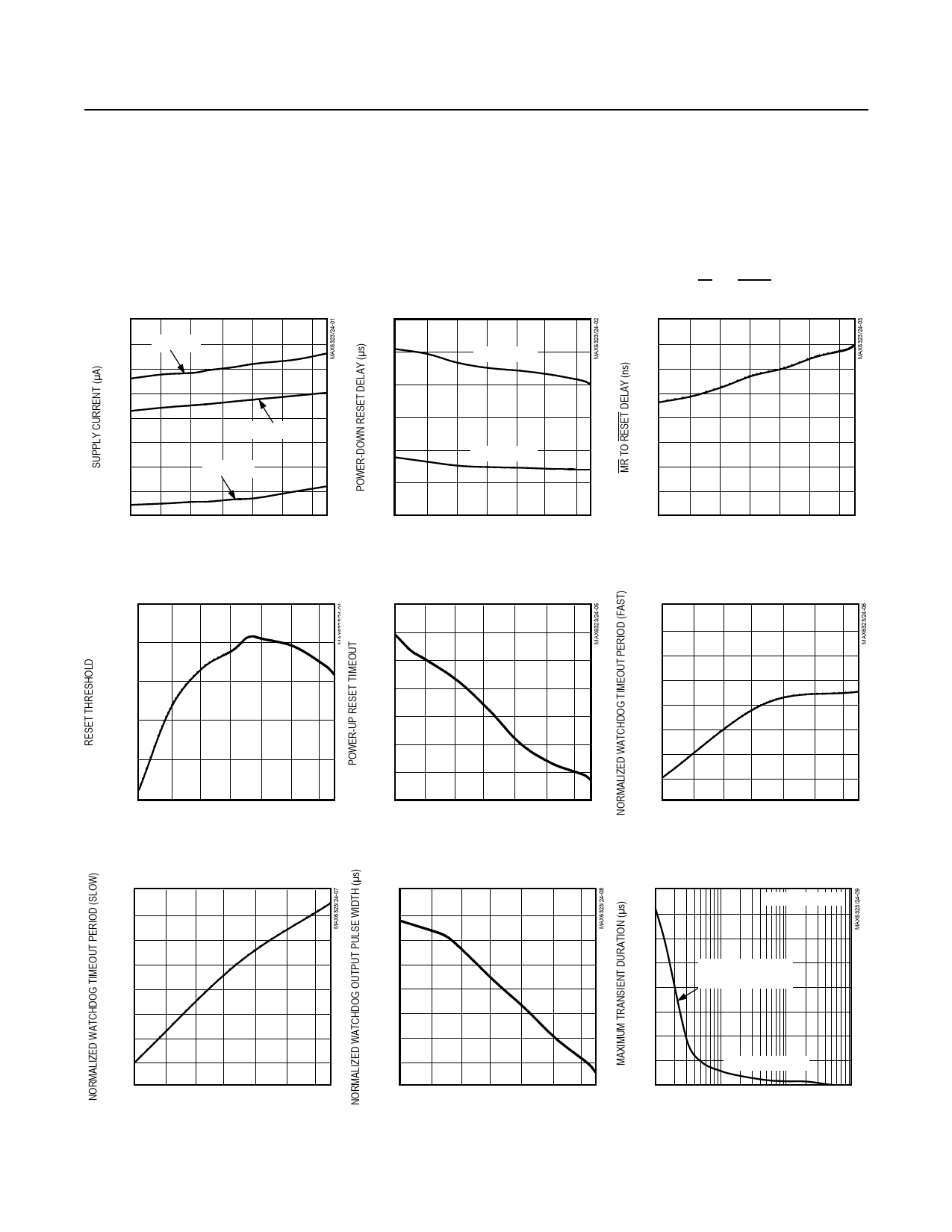

Typical Operating Characteristics (continued)

(VCC = full range, TA = +25°C, unless otherwise noted.)

FAST WATCHDOG TIMEOUT PERIOD

MAX6323/24-10

SLOW WATCHDOG TIMEOUT PERIOD

MAX6323/24-11

WDI

2V/div

WDI

2V/div

WDPO

2V/div WDPO

MAX6323AUT23

500µs/div

2V/div

MAX6323AUT23

5ms/div

Pin Description

PIN NAME

FUNCTION

Active-Low, Manual Reset Input. When MR is asserted low, RESET is asserted low, the internal watchdog

1

MR

timer is reset to zero, and WDPO is reset to high impedance (open drain). After the rising edge of MR,

RESET is asserted for at least 100ms. Leave MR unconnected or connect to VCC if unused.

2

GND Ground

Watchdog Input. The internal watchdog timer clears to zero on the falling edge of WDI or when RESET goes

3

WDI

high. If WDI sees another falling edge within the factory-trimmed watchdog window, WDPO will remain

unasserted. Transitions outside this window, either faster or slower, will cause WDPO to pulse low for 1ms

(typ).

4

VCC

Supply Voltage for the Device. Input for VCC reset monitor. For noisy systems, bypass VCC with a 500pF

(min) capacitor.

5

WDPO

Watchdog Pulse Output. The open-drain WDPO output is pulsed low for 1ms (typ) upon detection of a fast

or slow watchdog fault. WDPO is only active when RESET is high.

Active-Low. Reset is asserted when VCC drops below VTH and remains asserted until VCC rises above VTH

6

RESET for the duration of the reset timeout period. The MAX6323 has a push-pull output and the MAX6324 has an

open-drain output. Connect a pullup resistor from RESET to any supply voltage up to +6V.

_______________________________________________________________________________________ 5