MAX6956 데이터 시트보기 (PDF) - Maxim Integrated

부품명

상세내역

제조사

MAX6956

MAX6956 Datasheet PDF : 24 Pages

| |||

2-Wire-Interfaced, 2.5V to 5.5V, 20-Port or

28-Port LED Display Driver and I/O Expander

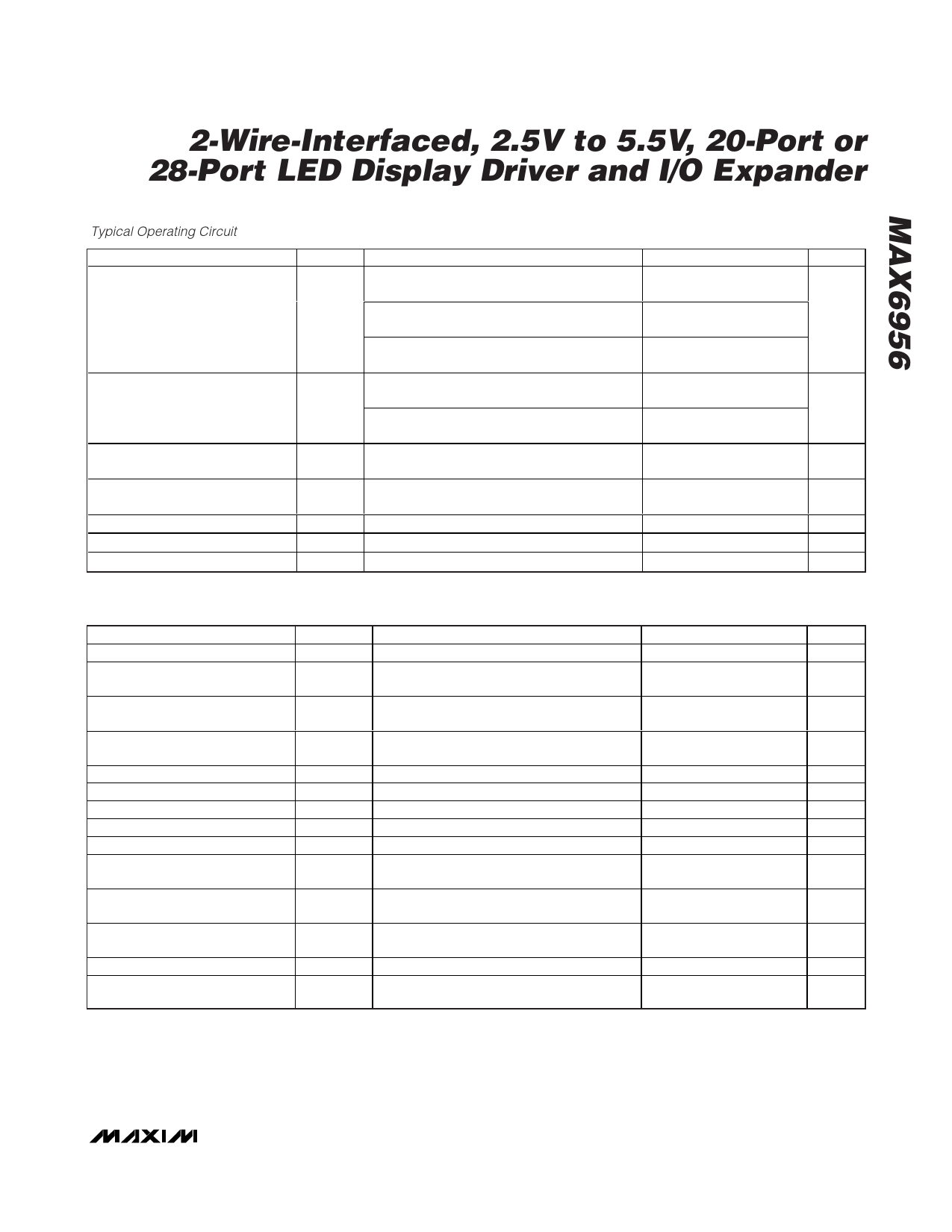

ELECTRICAL CHARACTERISTICS (continued)

(Typical Operating Circuit, V+ = 2.5V to 5.5V, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

PARAMETER

Port Drive LED Sink Current,

Port Configured as LED Driver

Port Drive Logic Sink Current,

Port Configured as LED Driver

Input High-Voltage SDA, SCL,

AD0, AD1

Input Low-Voltage SDA, SCL,

AD0, AD1

Input Leakage Current SDA, SCL

Input Capacitance

Output Low-Voltage SDA

SYMBOL

CONDITIONS

V+ = 2.5V, VLED = 2.3V at maximum LED

current

IDIGIT

V+ = 3.3V, VLED = 2.4V at maximum LED

current (Note 2)

V+ = 5.5V, VLED = 2.4V at maximum LED

current

IDIGIT_SC

V+ = 2.5V, VOUT = 0.6V at maximum sink

current

V+ = 5.5V, VOUT = 0.6V at maximum sink

current

VIH

VIL

IIH, IIL

VOL

(Note 2)

ISINK = 6mA

MIN TYP MAX UNITS

9.5

13.5

18

18.5

24

27.5

mA

19

25

30

18.5

23

28

mA

19

24

28

0.7 ✕

V+

-50

V

0.3 ✕

V

V+

50

nA

10

pF

0.4

V

TIMING CHARACTERISTICS (Figure 2)

(V+ = 2.5V to 5.5V, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN TYP MAX UNITS

Serial Clock Frequency

fSCL

400

kHz

Bus Free Time Between a STOP

and a START Condition

tBUF

1.3

µs

Hold Time (Repeated) START

Condition

tHD, STA

0.6

µs

Repeated START Condition

Setup Time

tSU, STA

0.6

µs

STOP Condition Setup Time

tSU, STO

0.6

µs

Data Hold Time

tHD, DAT (Note 3)

15

900

ns

Data Setup Time

tSU, DAT

100

ns

SCL Clock Low Period

tLOW

1.3

µs

SCL Clock High Period

tHIGH

0.7

µs

Rise Time of Both SDA and SCL

Signals, Receiving

tR

(Notes 2, 4)

20 +

300

ns

0.1Cb

Fall Time of Both SDA and SCL

Signals, Receiving

Fall Time of SDA Transmitting

tF

tF,TX

(Notes 2, 4)

(Notes 2, 5)

20 +

300

ns

0.1Cb

20 +

250

ns

0.1Cb

Pulse Width of Spike Suppressed

tSP

(Notes 2, 6)

0

50

ns

Capacitive Load for Each Bus

Line

Cb

(Note 2)

400

pF

Note 1: All parameters tested at TA = +25°C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: A master device must provide a hold time of at least 300ns for the SDA signal (referred to VIL of the SCL signal) in order to

bridge the undefined region of SCL’s falling edge.

Note 4: Cb = total capacitance of one bus line in pF. tR and tF measured between 0.3V+ and 0.7V+.

Note 5: ISINK ≤ 6mA. Cb = total capacitance of one bus line in pF. tR and tF measured between 0.3V+ and 0.7V+.

Note 6: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

_______________________________________________________________________________________ 3