MC145506 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

제조사

MC145506 Datasheet PDF : 24 Pages

| |||

Freescale Semiconductor, Inc.

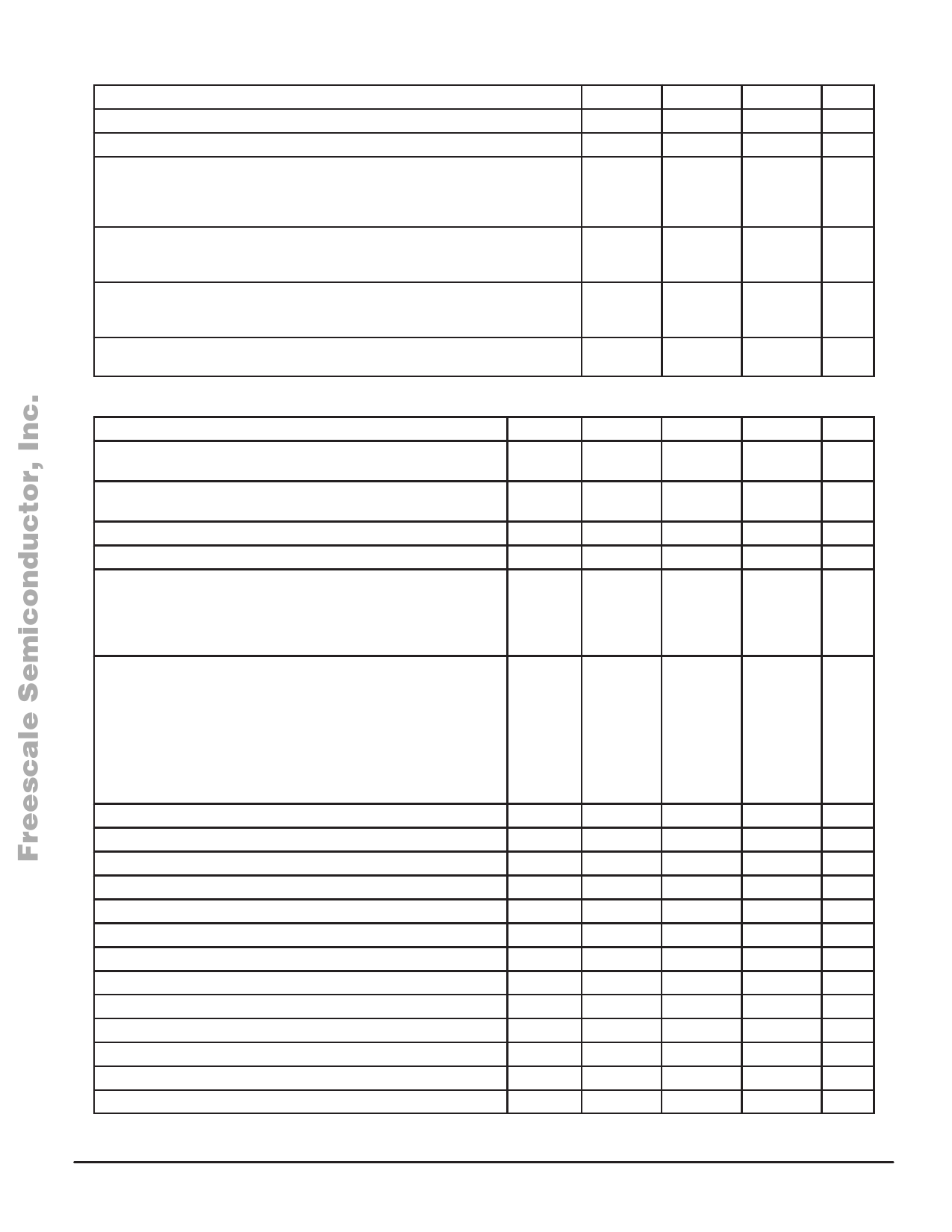

MODE CONTROL LOGIC (VSS to VDD = 4.75 V to 12.6 V, TA = –40° to 85°C)

Characteristic

Min

Typ

VLS Voltage for HCMOS Mode (HCMOS Logic Levels Referenced to VLS)

VSS

—

VLS Voltage for CMOS Mode (CMOS Logic Levels of VSS to VDD)

VDD – 0.5

—

Mu/A Select Voltage

Mu–Law Mode VDD – 0.5

—

Sign Magnitude Mode VAG – 0.5

—

A–Law Mode

VSS

—

RSI Voltage for Reference Select Input (MC145506)

3.78 V Mode VDD – 0.5

—

2.5 V Mode VAG – 0.5

—

3.15 V Mode

VSS

—

Vref Voltage for Internal or External Reference (MC145506 Only)

Internal Reference Mode

VSS

—

External Reference Mode VAG + 0.5

—

Analog Test Mode Selection Frequency, MS = CCI (MC145506 Only)

See Pin Description; Test Modes

—

128

Max

Unit

VDD – 4.0

V

VDD

V

V

VDD

VAG + 0.5

VSS + 0.5

VDD

V

VAG + 0.5

VSS + 0.5

V

VSS + 0.5

VDD – 1.0

—

kHz

SWITCHING CHARACTERISTICS (VSS to VDD = 9.5 V to 12.6 V, TA = –40° to 85°C, CL = 150 pF, CMOS or HCMOS Mode)

Characteristic

Symbol

Min

Typ

Max

Unit

Output Rise Time

Output Fall Time

TDD tTLH

—

30

80

ns

tTHL

—

30

80

Input Rise Time

Input Fall Time

TDE, TDC, RCE, RDC, DC, MSI, CCI tTLH

—

—

tTHL

—

—

4

µs

4

Pulse Width

TDE Low, TDC, RCE, RDC, DC, MSI, CCI

tw

100

—

—

ns

Data Clock Pulse Frequency

TDC, RDC, DC

fCL

64

—

4096

kHz

CCI Clock Pulse Frequency (MSI = 8 kHz)

fCL1

—

128

—

kHz

This Pin Will Accept One of These Discrete Clock Frequencies and

fCL2

—

1536

—

Will Compensate to Produce Internal Sequencing

fCL3

—

1544

—

fCL4

—

2048

—

fCL5

—

2560

—

Propagation Delay Time

TDE Rising to TDD Low Impedance

TDE Falling to TDD High Impedance

TDC Rising Edge to TDD Data, During TDE High

TDE Rising Edge to TDD Data, During TDC High

HCMOS

tP1

—

CMOS

—

HCMOS

tP2

—

CMOS

—

HCMOS

tP3

—

CMOS

—

HCMOS

tP4

—

CMOS

—

ns

90

180

90

150

—

55

—

40

90

180

90

150

90

180

90

150

TDC Falling Edge to TDE Rising Edge Setup Time

tsu1

20

—

—

ns

TDE Rising Edge to TDC Falling Edge Setup Time

tsu2

100

—

TDE Falling Edge to TDC Rising Edge to Preserve the Next TDD Data

tsu8

20

—

—

ns

—

ns

RDC Falling Edge to RCE Rising Edge Setup Time

RCE Rising Edge to RDC Falling Edge Setup Time

RDD Valid to RDC Falling Edge Setup Time

tsu3

20

—

tsu4

100

—

tsu5

60

—

—

ns

—

ns

—

ns

CCI Falling Edge to MSI Rising Edge Setup Time

MSI Rising Edge to CCI Falling Edge Setup Time

RDD Hold Time from RDC Falling Edge

tsu6

20

—

tsu7

100

—

th

100

—

—

ns

—

ns

—

ns

TDE, TDC, RCE, RDC, RDD, DC, MSI, CCI Input Capacitance

—

—

10

pF

TDE,TDC, RCE, RDC, RDD, DC, MSI, CCI Input Current

—

±0.01

±0.2

µA

TDD Capacitance During High Impedance (TDE Low)

—

12

15

pF

TDD Input Current During High Impedance (TDE Low)

—

±0.1

±10.0

µA

MC145506•MC145507•MC14550F8or More Information On This Product,

6

Go to: www.freescale.com

MOTOROLA