IDT49C466A 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

제조사

IDT49C466A Datasheet PDF : 27 Pages

| |||

IDT49C466/A Flow-thruEDC™

ERROR DETECTION AND CORRECTION UNIT

COMMERCIAL TEMPERATURE RANGES

DETAILED DESCRIPTION —

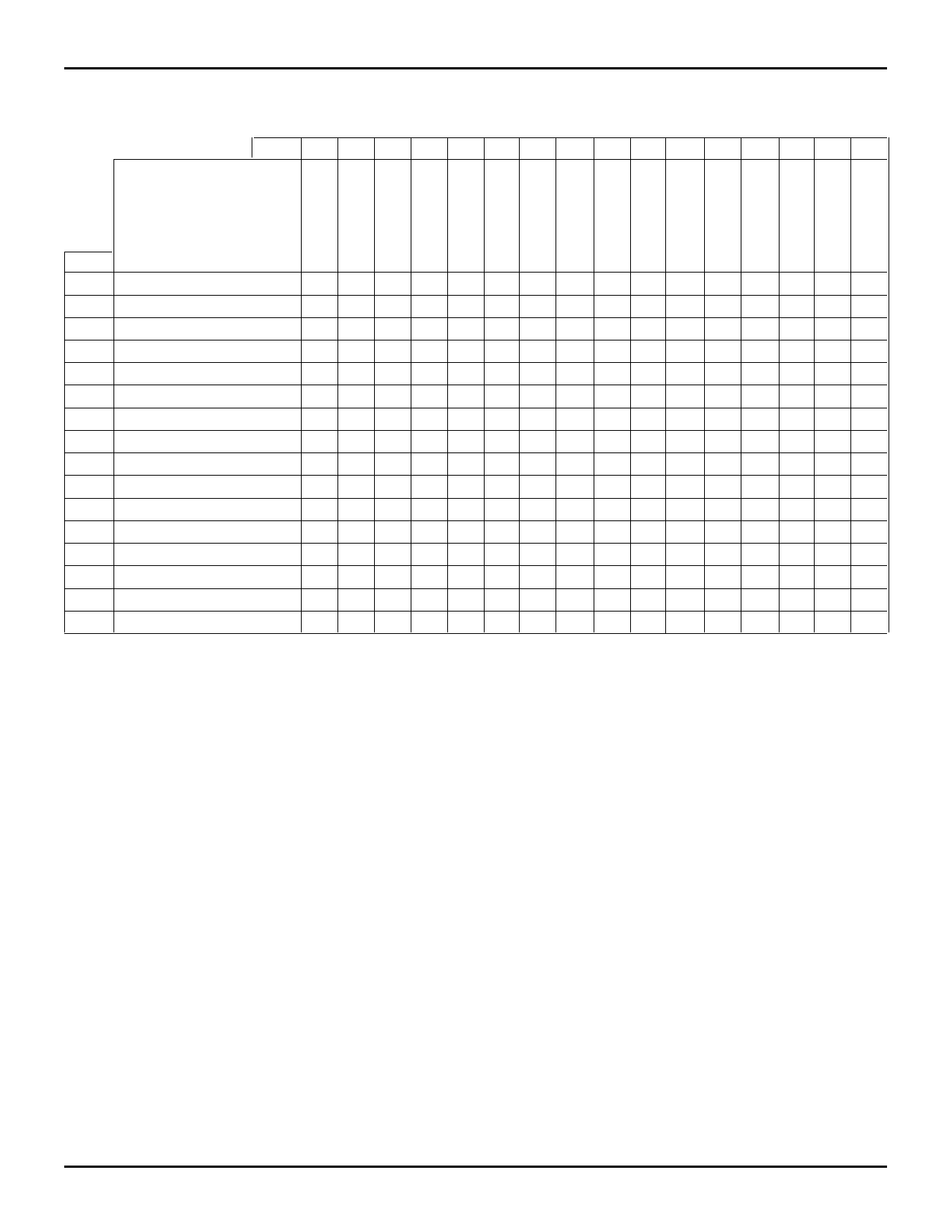

64-BIT SYNDROME DECODE TO BIT-IN-ERROR(1)

HEX 0 1 2 3 4 5 6 7 8 9 A B C D E F

S7 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

S6 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

Syndrome

S5 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

Bits

S4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

HEX S3 S2 S1 S0

00000

* C4 C5 T C6 T T 62 C7 T T 46 T M M T

10001

C0 T T 14 T M M T T M M T M T T 30

20010

C1 T T M T 34 56 T T 50 40 T M T T M

30011

T 18 8 T M T T M M T T M T 2 24 T

40100

C2 T T 15 T 35 57 T T 51 41 T M T T 31

50101

T 19 9 T M T T 63 M T T 47 T 3 25 T

60110

T 20 10 T M T T M M T T M T 4 26 T

70111

M T T M T 36 58 T T 52 42 T M T T M

81000

C3 T T M T 37 59 T T 53 43 T M T T M

91001

T 21 11 T M T T M M T T M T 5 27 T

A1010

T 22 12 T 33 T T M 49 T T M T 6 28 T

B1011

17 T T M T 38 60 T T 54 44 T 1 T T M

C1100

T 23 13 T M T T M M T T M T 7 29 T

D1101

M T T M T 39 61 T T 55 45 T M T T M

E1110

16 T T M T M M T T M M T 0 T T M

F1111

T M M T 32 T T M 48 T T M T M M T

NOTES:

2617 tbl 07

1. The table indicates the decoding of the eight syndrome bits to identify the bit-in-error for a single-bit error, or whether a double or triple-bit error was detected.

The all-zero case indicates no error detected.

* = No errors detected

# = The number of the single data bit-in-error

T = Two errors detected

M = Three or more detected

C# = The number of the single checkbits in error

IDT49C466 OPERATION

The EDC is involved in two types of operation — memory

reads and memory writes. With the IDT49C466, both these

can be accomplished by utilizing either of two possible data

paths — one incorporating the FIFO and the other without the

FIFO. These operations are treated separately below.

Memory Write

The involvement of the EDC in this type of operation is

relatively minimal since it does not call for any error checking.

It only generates the check bits associated with each 64-bit

wide data word. The EDC can be in generate-detect or normal

mode for this operation.

When a write operation is performed, it must be ensured

that the SD output buffer (enabled by SOE and BE0-7) is

disabled so that no attempt is made to simultaneously transfer

read data onto the System Data (SD) Bus.

When the write FIFO (WFIFO) is bypassed (WBSEL

LOW), data passes through the SD Latch In. To latch data, the

SDILE signal should be pulled LOW. The special case of a

partial word write or byte merge is discussed later. Here it is

assumed that all 64 bits are being written. Consequently,

BE0-7 must all be LOW.

The data is fed to the SD Checkbit generator where

appropriate checkbits are generated. Both system data and

the generated checkbits can be latched by pulling the SDOLE

signal HIGH. Asserting MOE enables the MD output buffer

and data is output to the Memory Data (MD) bus. CBSEL (=1)

or MOE(=0) need to be asserted to enable the CBSYN output

buffer and output checkbits on CBSYN0-7.

When the write FIFO is selected (WBSEL = 1), instead of

asserting SDILE, WBEN is asserted and data is clocked into

the write FIFO on the rising edge of SCLK. WBFF is asserted

when the WFIFO is full and this inhibits further write attempts

(see section on "Clock Skew" and "R/W FIFO Operation at

Boundaries") to the WFIFO. When WBREN is asserted, data

can be clocked out of the write FIFO on the rising edge of

MCLK. WBEF is asserted when the WFIFO is empty and this

inhibits further read attempts (see section on "Clock Skew")

from the WFIFO.

11.7

7