MT9040 데이터 시트보기 (PDF) - Zarlink Semiconductor Inc

부품명

상세내역

제조사

MT9040 Datasheet PDF : 27 Pages

| |||

MT9040

Data Sheet

Control and Mode of Operation

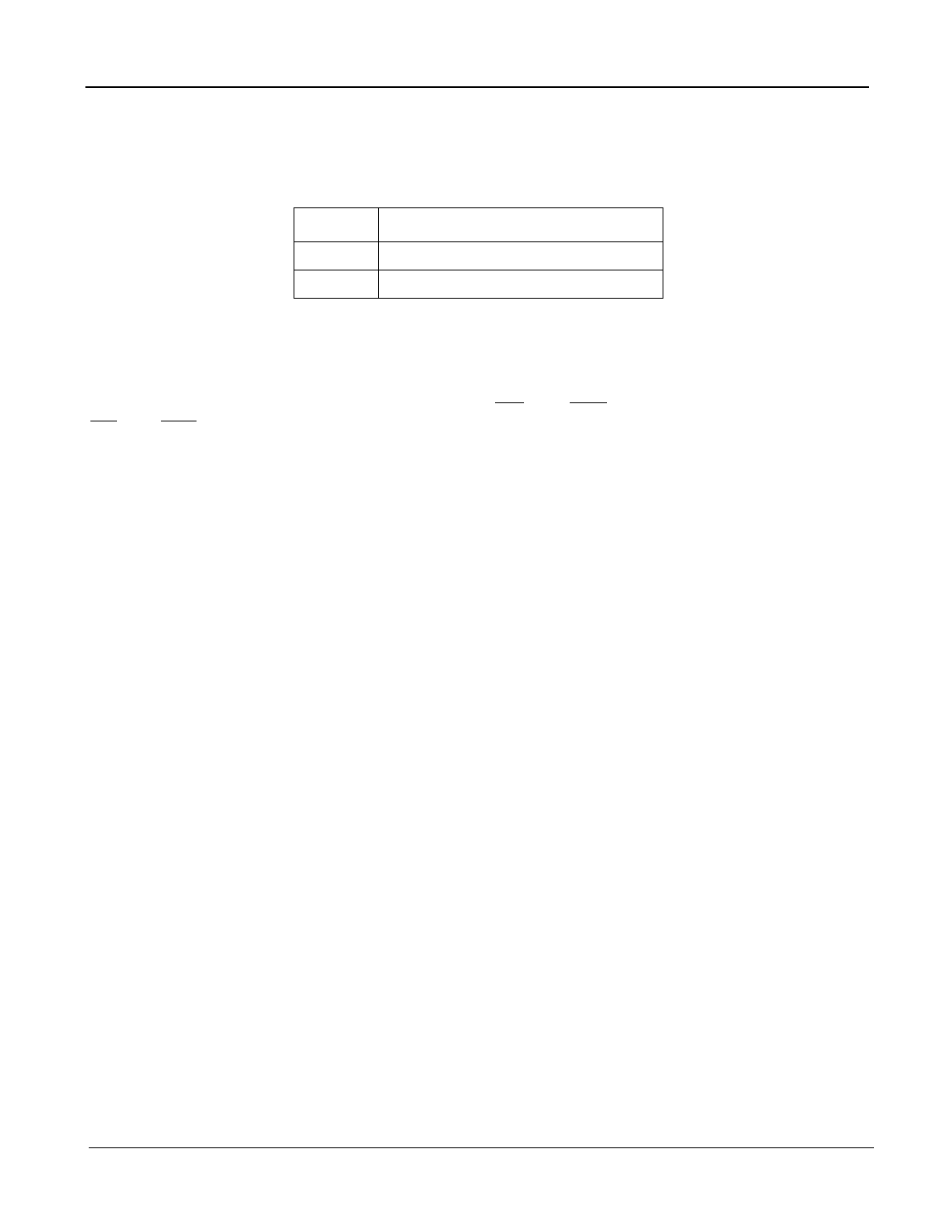

The MT9040 has two possible modes of operation, Normal and Freerun. As shown in Table 2, the Mode/Control

Select pin MS selects the mode.

MS

Mode

0

NORMAL

1

FREERUN

Table 2 - Operating Modes and States

Normal Mode

Normal Mode is typically used when a slave clock source, synchronized to the network is required.

In Normal Mode, the MT9040 provides timing (C1.5o, C2o, C4o, C8o, C16o and C19o) and frame synchronization

(F0o, F8o, F16o, TSP and RSP) signals, which are synchronized to the reference input. The input reference signal

may have a nominal frequency of 8kHz, 1.544MHz, 2.048MHz or 19.44MHz.

From a reset condition, the MT9040 will take up to 30 seconds (see AC Electrical Characteristics) of input reference

signal to output signals which are synchronized (phase locked) to the reference input.

The reference frequencies are selected by the frequency control pins FS2 and FS1 as shown in Table 1.

Fast Lock Mode

Fast Lock Mode is a submode of Normal Mode, it is used to allow the MT9040 to lock to a reference more quickly

than Normal mode will allow. Typically, the PLL will lock to the incoming reference within 500 ms if the FLOCK pin is

set high.

Freerun Mode

Freerun Mode is typically used when a master clock source is required, or immediately following system power-up

before network synchronization is achieved.

In Freerun Mode, the MT9040 provides timing and synchronization signals which are based on the master clock

frequency (OSCi) only, and are not synchronized to the reference signal.

The accuracy of the output clock is equal to the accuracy of the master clock (OSCi). So if a ±32ppm output clock

is required, the master clock must also be ±32ppm. See Applications - Crystal and Clock Oscillator sections.

MT9040 Measures of Performance

The following are some synchronizer performance indicators and their corresponding definitions.

Intrinsic Jitter

Intrinsic jitter is the jitter produced by the synchronizing circuit and is measured at its output. It is measured by

applying a reference signal with no jitter to the input of the device, and measuring its output jitter. Intrinsic jitter may

also be measured when the device is free running by measuring the output jitter of the device. Intrinsic jitter is

usually measured with various bandlimiting filters depending on the applicable standards. In the MT9040, the

intrinsic Jitter is limited to less than 0.02UI on the 2.048MHz and 1.544MHz clocks.

7

Zarlink Semiconductor Inc.