MX29F1611 데이터 시트보기 (PDF) - Macronix International

부품명

상세내역

제조사

MX29F1611 Datasheet PDF : 36 Pages

| |||

INDEX

MX29F1611

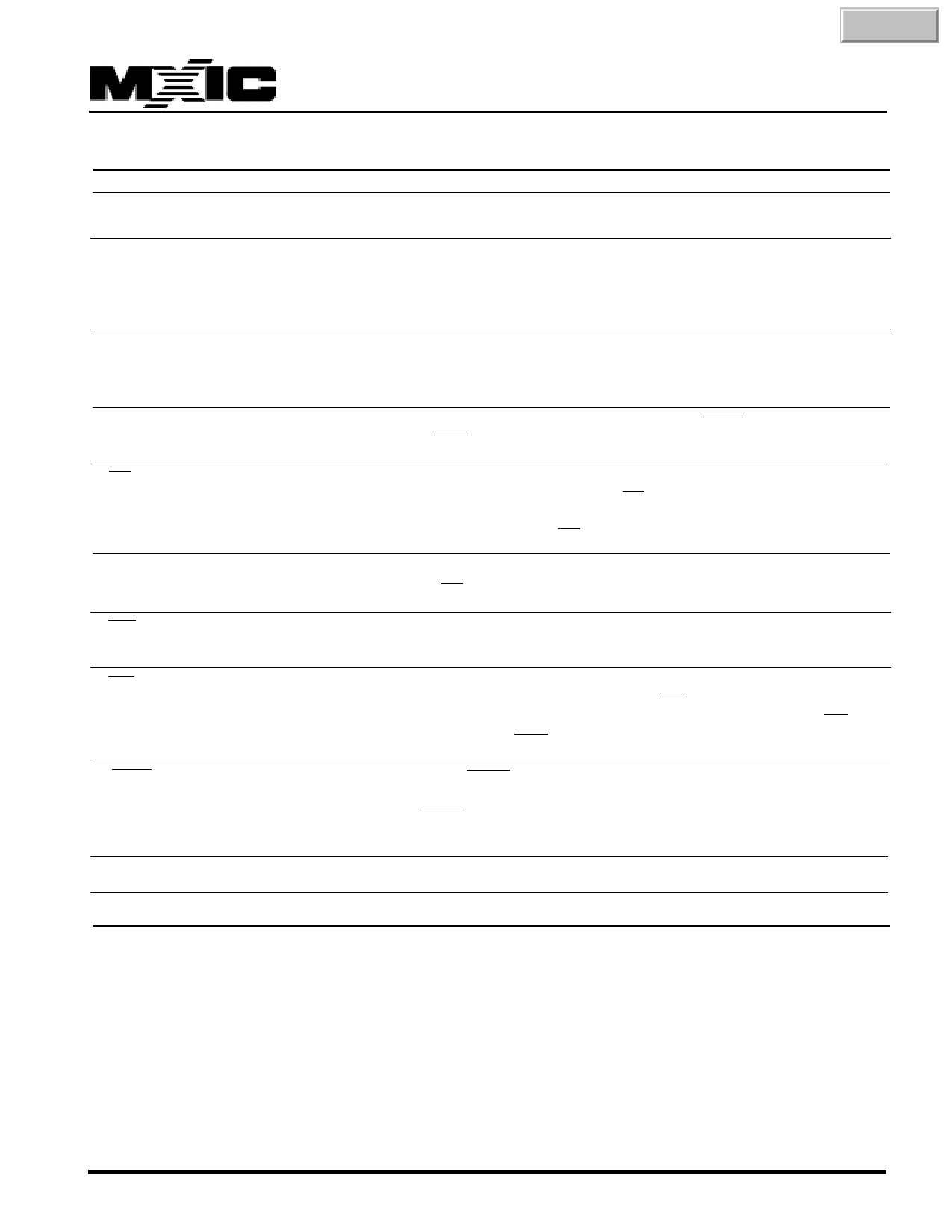

Table1.PIN DESCRIPTIONS

SYMBOL

TYPE

A0 - A19 INPUT

NAME AND FUNCTION

ADDRESS INPUTS: for memory addresses. Addresses are internally latched

during a write cycle.

Q0 - Q7

INPUT/OUTPUT

LOW-BYTE DATA BUS: Input data and commands during Command Interface

Register(CIR) write cycles. Outputs array,status and identifier data in the

appropriate read mode. Floated when the chip is de-selected or the outputs are

disabled.

Q8 - Q14

.

Q15/A -1

INPUT/OUTPUT

HIGH-BYTE DATA BUS: Inputs data during x 16 Data-Write operations. Outputs

array, identifier data in the appropriate read mode; not used for status register

reads. Floated when the chip is de-selected or the outputs are disabled

INPUT/OUTPUT Selects between high-byte data INPUT/OUTPUT(BYTE = HIGH) and LSB

ADDRESS(BYTE = LOW)

CE

INPUT

CHIP ENABLE INPUTS: Activate the device's control logic, Input buffers,

decoders and sense amplifiers. With CE high, the device is deselected and

power consumption reduces to Standby level upon completion of any current

program or erase operations. CE must be low to select the device.

OE

INPUT

OUTPUT ENABLES: Gates the device's data through the output buffers during

a read cycle OE is active low.

WE

INPUT

WRITE ENABLE: Controls writes to the Command Interface Register(CIR). WE

is active low.

WP

INPUT

WRITE PROTECT: Top or Bottom sector can be protected by writing a non-

volatile protect-bit for each sector. When WP is high, all sectors can be

programmed or erased regardless of the state of the protect-bits. The WP input

buffer is disabled when PWD transitions low(deep power-down mode).

BYTE

INPUT

BYTE ENABLE: BYTE Low places device in x8 mode. All data is then input or

output on Q0-7 and Q8-14 float. AddressQ15/A-1 selects between the high and

low byte. BYTE high places the device in x16 mode, and turns off the Q15/A-1

input buffer. Address A0, then becomes the lowest order address.

VCC

DEVICE POWER SUPPLY(5V± 5%)

GND

GROUND

P/N: PM0440

REV. 1.6, JUL. 16, 1998

4