PBM3960-1NS 데이터 시트보기 (PDF) - Ericsson

부품명

상세내역

제조사

PBM3960-1NS Datasheet PDF : 10 Pages

| |||

PBM 3960/1

Vref 1

22 Reset

DA1 2

Sign 1 3

21 DA2

20 Sign 2

CD 1 4

19 CD 2

PBM VDD 5

18 VSS

WR 6 3960/1N 17 CS

D7 7

16 A1

D6 8

15 A0

D5 9

14 D0

D4 10

13 D1

D3 11

12 D2

N/C 5

DA 2 6

Reset 7

N/C 8

Vref 9

DA1 10

N/C 11

PBM

3960/1QN

25 D0

24 D1

23 D2

22 N/C

21 D3

20 D4

19 D5

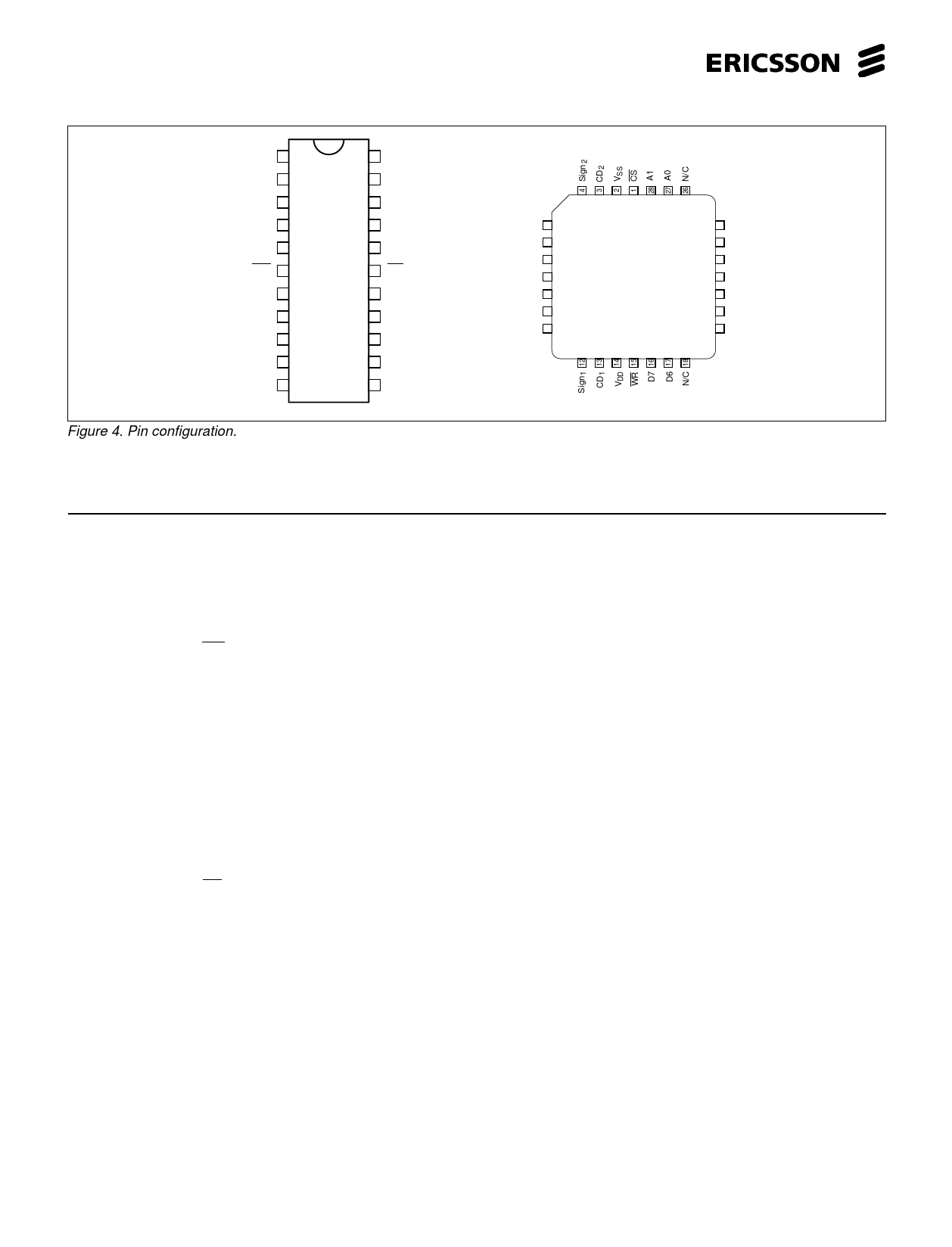

Figure 4. Pin configuration.

Pin Descriptions

Refer to figure 4.

DIP

PLCC

1

9

2

10

3

12

Symbol

VRef

DA1

Sign1

4

13

CD1

5

14

VDD

6

15

WR

7

16

D7

8

17

D6

9

19

D5

10

20

D4

11

21

D3

12

23

D2

13

24

D1

14

25

D0

15

27

A0

16

28

A1

17

1

CS

18

2

19

3

20

4

21

6

22

7

V

SS

CD2

Sign2

DA2

Reset

5

8

11

18

22

26

4

Description

Voltage reference supply pin, 2.5 V nominal (3.0 V maximum)

Digital-to-Analog 1, voltage output. Output between 0.0 V and VR - 1 LSB.

Sign 1, TTL/CMOS level. To be connected directly to PBL 3771 Phase input.

Databit D7 is transfered non inverted from PBM 3960/1/1 data input.

Current Decay 1, TTL/CMOS level. The signal is automatically generated when

decay level is programmed. LOW level = fast current decay.

Voltage Drain-Drain, logic supply voltage. Normally +5 V.

Write, TTL/CMOS level, input for writing to internal registers.

Data is clocked into flip flops on positive edge.

Data 7, TTL/CMOS level, input to set data bit 7 in data word.

Data 6, TTL/CMOS level, input to set data bit 6 in data word.

Data 5, TTL/CMOS level, input to set data bit 5 in data word.

Data 4, TTL/CMOS level, input to set data bit 4 in data word.

Data 3, TTL/CMOS level, input to set data bit 3 in data word.

Data 2, TTL/CMOS level, input to set data bit 2 in data word.

Data 1, TTL/CMOS level, input to set data bit 1 in data word.

Data 0, TTL/CMOS level, input to set data bit 0 in data word.

Address 0, TTL/CMOS level, input to select data transfer,

A0 selects between cannel 1 (A0 = LOW) and channel 2 (A0 = HIGH).

Address 1, TTL/CMOS level, input to select data transfer. A1 selects between normal

D/A register programming (A1 = LOW) and decay level register programming (A1 = HIGH).

Chip Select, TTL/CMOS level, input to select chip and activate data transfer

from data inputs. LOW level = chip is selected.

Voltage Source-Source. Ground pin, 0 V reference for all signals and

measurements unless otherwise noted.

Current Decay 2, TTL/CMOS level. The signal is automatically generated

when decay level is programmed. LOW level = fast current decay .

Sign 2. TTL/CMOS level. To be connected directly to PBL 3771 sign input.

Data bit D7 is transfered non-inverted from PBM 3960/1 data input.

Digital-to-Analog 2, voltage output. Output between 0.0 V and Vref - 1 LSB.

Reset, digital input resetting internal registers.

HIGH level = Reset, VRes ≥ 3.5 V = HIGH level. Pulled low internally.

Not Connected

Not Connected

Not Connected

Not Connected

Not Connected

Not Connected