MSM80C88A-10GS-K 데이터 시트보기 (PDF) - Oki Electric Industry

부품명

상세내역

제조사

MSM80C88A-10GS-K Datasheet PDF : 37 Pages

| |||

¡ Semiconductor

MSM80C88A-10RS/GS/JS

Bus Operation

The MSM80C88A-10 has a time multiplexed address and data bus. If a non-multiplexed bus is

desired for the system, it is only needed to add the address latch.

A CPU bus cycle consists of at least four clock cycles: T1, T2, T3 and T4. (Fig. 4)

The address output occurs during T1, and data transfer occurs during T3 and T4. T2 is used for

changing the direction of the bus during read operation. When the device which is accessed by

the CPU is not ready to data transfer and send to the CPU “NOT READY” is indicated TW cycles

are inserted between T3 and T4.

When a bus cycle is not needed, T1 cycles are inserted between the bus cycles for internal

execution. At the T1 cycle an ALE signal is output from the CPU or the MSM82C88-2 depending

in MN/MX, at the trailing edge of an ALE, a valid address may be latched. Status bits S0, S1 and

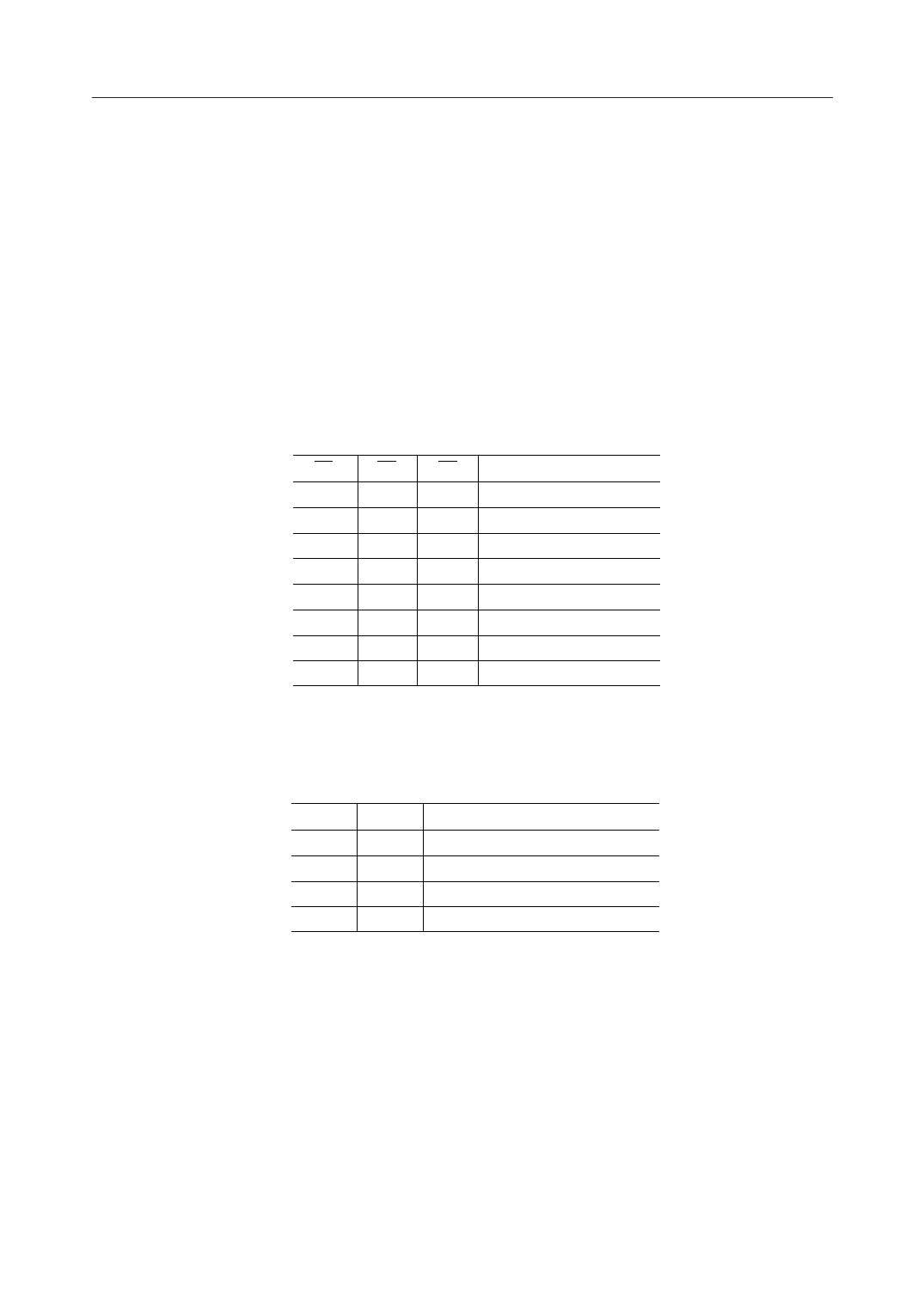

S2 are used, in maximum mode, by the bus controller to recognize the type of bus operation

according to the following table.

S2

S1

0 (LOW) 0

0

0

0

1

0

1

1 (HIGH) 0

1

0

1

1

1

1

S0

Characteristics

0 Interrupt acknowledge

1 Read I/O

0 Write I/O

1 Halt

0 Instruciton Fetch

1 Read Data from Memory

0 Write Data to Memory

1 Passive (no bus cycle)

Status bits S3 through S6 are multiplexed with A16-A19, and therefore they are valid during T2

through T4. S3 and S4 indicate which segment register was selected on the bus cycle, according

to the following table.

S4

S3

0 (LOW) 0

0

1

1 (HIGH) 0

1

1

Characteristics

Alternate Data (Extra Segment)

Stack

Code or None

Data

S5 indicates interrupt enable Flag.

I/O Addressing

The MSM80C88A-10 has a 64 Kbyte I/O. When the CPU accesses an I/O device, addresses A0-

A15 are in same format as a memory access, and A16-A19 are low.

I/O ports addresses are same as four memory.

21/37