PLL130-07 데이터 시트보기 (PDF) - PhaseLink Corporation

부품명

상세내역

제조사

PLL130-07 Datasheet PDF : 5 Pages

| |||

PLL130-07

High Speed Translator Buffer to CMOS (Selectable Drive)

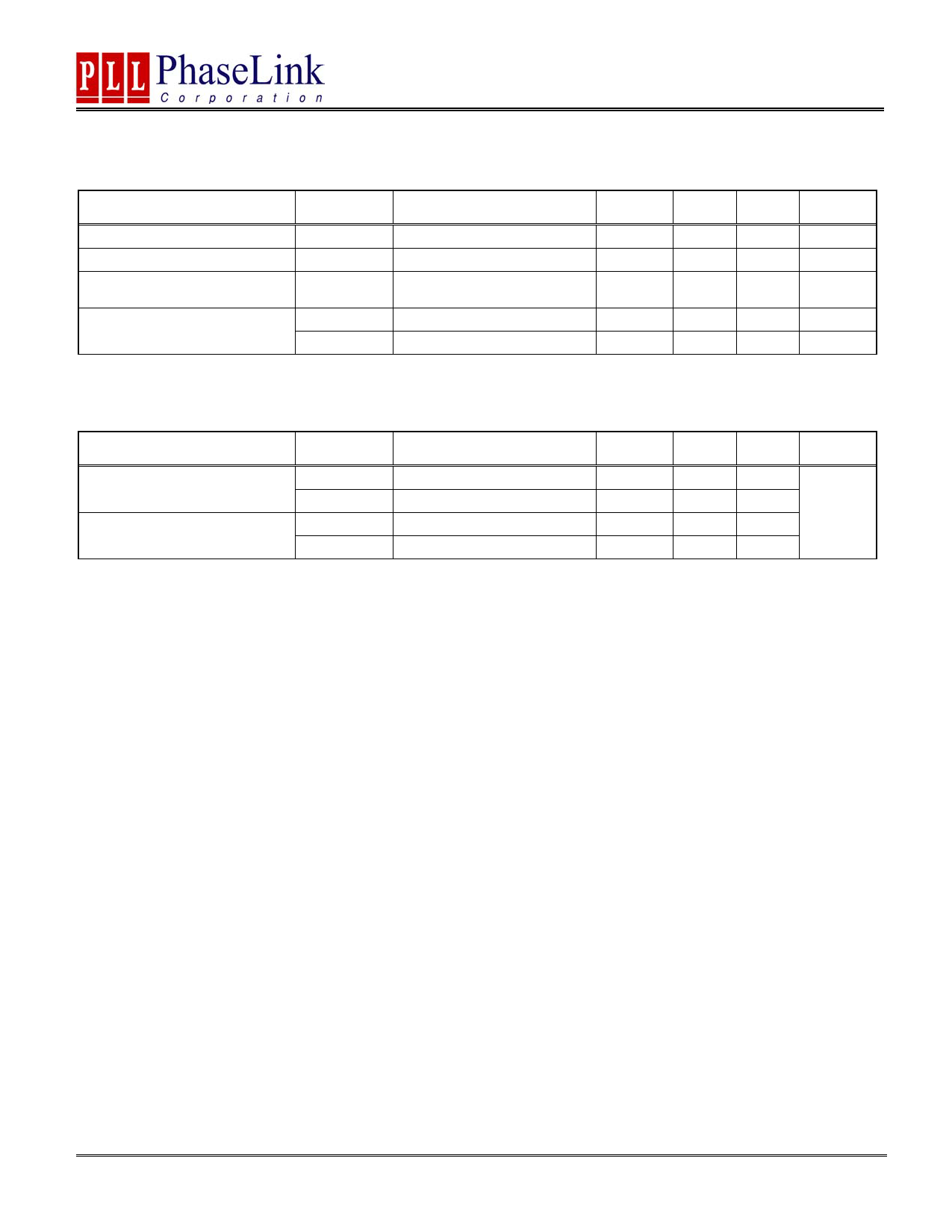

3. CMOS Output Electrical Specifications

PARAMETERS

SYMBOL

CONDITIONS

MIN.

Output High Voltage

Output Low Voltage

Output High Voltage at CMOS

level

Output drive current

VOH

IOH = -12mA

2.4

VOL

ILO = 12mA

VOHC

IOH = -4mA

VDD– 0.4

At TTL level (High drive*)

36

At TTL level (Standard drive)

12

* Note: High Drive CMOS is selectable through DRIV_SEL selector input on pin 8(SOIC) or 13(QFN).

4. CMOS Switching Characteristics

TYP.

51

17

MAX.

0.4

UNITS

V

V

V

mA

mA

PARAMETERS

SYMBOL

CONDITIONS

MIN.

Output Clock Rise/Fall Time

Output Clock Rise/Fall Time

(High Drive*)

0.8V ~ 2.0V with 10 pF load

0.3V ~ 3.0V with 15 pF load

0.8V ~ 2.0V with 10 pF load

0.3V ~ 3.0V with 15 pF load

* Note: High Drive CMOS is selectable through DRIV_SEL selector input on pin 8(SOIC) or 13(QFN).

TYP.

1.15

3.7

0.5

1.5

MAX.

UNITS

ns

47745 Fremont Blvd., Fremont, California 94538 Tel (510) 492-0990 Fax (510) 492-0991 www.phaselink.com Rev 09/09/04 Page 3