PM3386-BI 데이터 시트보기 (PDF) - PMC-Sierra

부품명

상세내역

제조사

PM3386-BI Datasheet PDF : 315 Pages

| |||

RELEASED

DATASHEET

PMC-1991129

ISSUE 7

PM3386

DUAL GIGABIT ETHERNET CONTROLLER

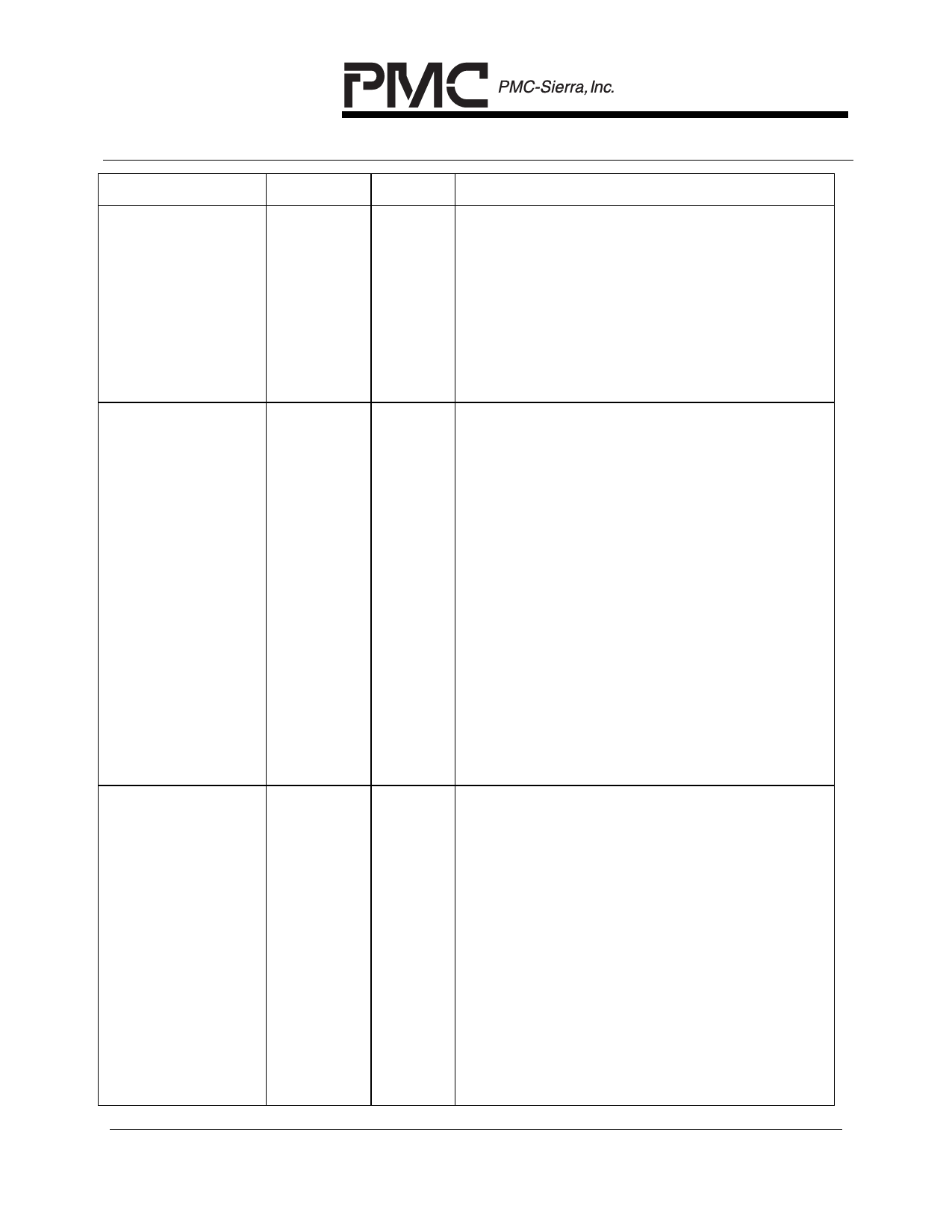

Signal Name

TERR

TENB

TPRTY

Direction

Input

Input

Input

Pin No.

AF5

AD8

AE6

Function

POS-PHY Transmit Error Indicator

Active high signal used to indicate that the

current packet must be aborted. TERR

should only be considered valid when

TENB and TEOP are simultaneously

asserted.

TERR is sampled on the rising edge of

TFCLK.

POS-PHY Transmit Write Enable

Active low signal used to control the flow of

data to the transmit FIFOs.

When TENB is high, the TDAT[31:0],

TMOD, TSOP, TEOP, TPRTY and TERR

signals are invalid and are ignored by the

PM3386. However, the TSX signal if

asserted is valid and is processed by the

PM3386 only when TENB is high.

When TENB is low, the TDAT[31:0], TMOD,

TSOP, TEOP, TPRTY and TERR signals

are valid and are processed by the

PM3386. The TSX signal is ignored by the

PM3386 when TENB is low.

TENB is sampled on the rising edge of

TFCLK.

POS-PHY Transmit bus parity

The transmit parity (TPRTY) signal

indicates the parity calculated over the

TDAT bus. TPRTY is considered valid only

when TENB or TSX are asserted.

By default the PM3386 uses odd parity.

The PM3386 supports both even and odd

parity. The PM3386 reports any parity error

to the host processor via a maskable

interrupt, but does not interfere with the

transferred data.

TPRTY is sampled on the rising edge of

TFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

23