RTL8181 데이터 시트보기 (PDF) - Realtek Semiconductor

부품명

상세내역

제조사

RTL8181 Datasheet PDF : 50 Pages

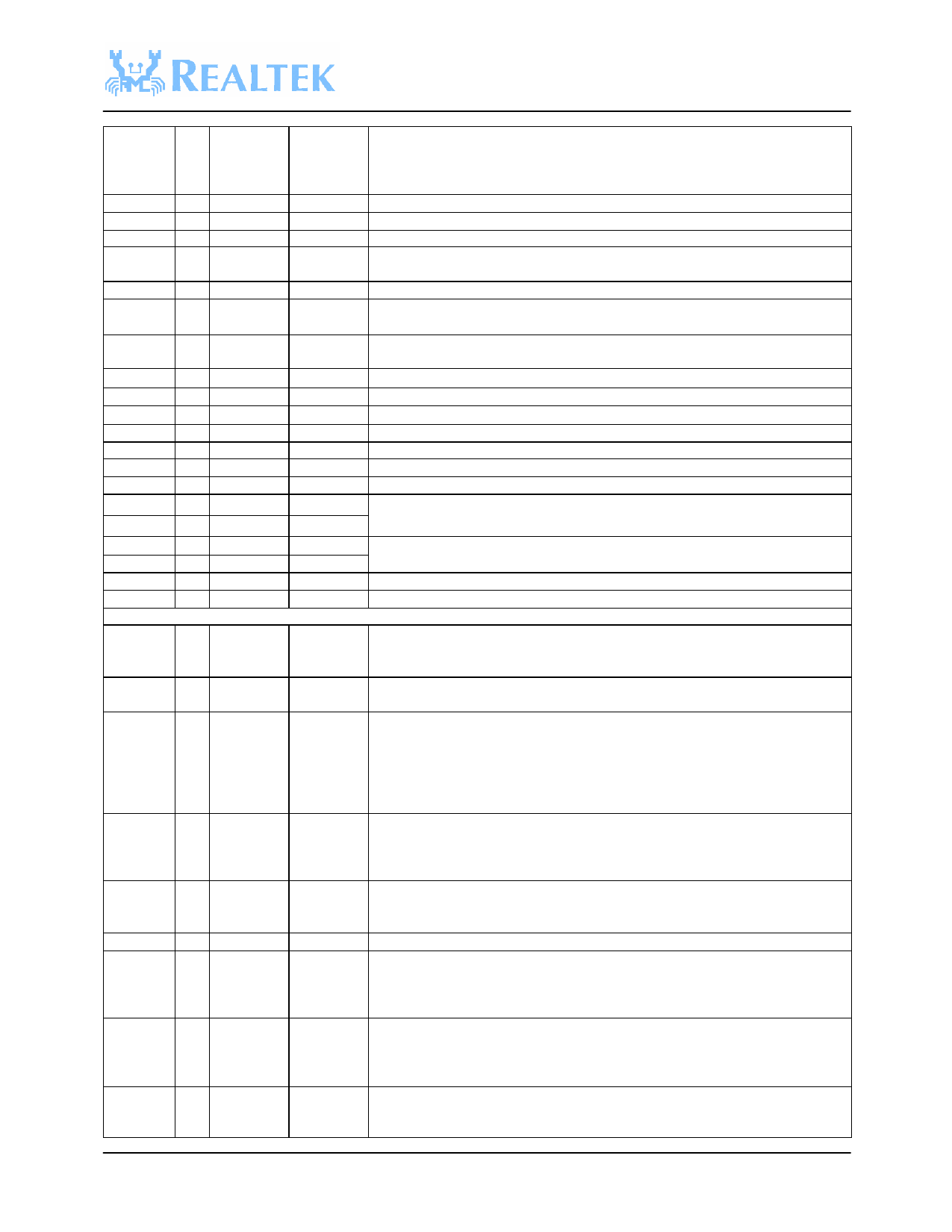

| |||

ANTSELP O 75

M20

ANTSELN X 76

L18

TRSWP X 78

L19

TRSWN X 79

L20

VCOPDN/ O/I 81

K20

PHITXI

PAPE O 82

K19

PE1/PHIT O 84

K18

XQ

PE2

O 85

J20

RXIP

AI* 110

B19

RXIN X 109

B20

RXQP AI 106

C18

RXQN X 105

C19

RSSI

X 103

D17

TXDET AI 102

D18

VREFI AI 101

C20

TXIP

AO 97

E19

TXIN AO 96

F18

TXQP AO 94

E20

TXQN AO 93

F20

TXAGC AO 91

F19

RXAGC AO 90

G18

RF Interface for Philip

RIFSCK O 66

R20

RIFSD O 67

P19

RFLE O 68

P18

IFLE/AGC I 70

N18

SET

CALEN/ O 71

P20

AGCRESE

T

LNA_HL X* 73

M19

ANTSELP O 75

M20

ANTSELN O 76

L18

TRSWP O 78

L19

CONFIDENTIAL

RTL8181

Antenna Select +: The antenna selects signal changes state as the receiver

switches from antenna to antenna during the acquisition process in the antenna

diversity mode. This is a complement for ANTSEL- for differential drive of

antenna switches.

Not used in the RFMD RF chipset.

Not used in the RFMD RF chipset.

Not used in the RFMD RF chipset.

Output Pin as VCO VCC Power Enable/D isable.

Power Control Output for RF2189 PA: 0V to +3.3V.

This pin is the shutdown control output on board regulator when the RF Module

enters either power-saving or standby mode.

Output pin as RF2948 RX EN/ TX EN, RF2494 OE and CE:

Refer to the RF2948 and RF2494 datasheets.

Receive (Rx) In-phase Analog Data in Single Ended

Not used in RFMD RF chipset.

Receive (Rx) Quadrature-phase Analog Data in Single Ended

Not used in RFMD RF chipset.

Not used in RFMD RF chipset.

To internal ADC which detects transmit power.

Reference voltage for ADC, DAC from VREF1 of RF2948B.

Transmit (TX) In-phase Digital Data:Combining before connecting to TX_I of

RF2948B.

Transmit (TX) Quadrature Digital Data: Combining before connecting to TX_Q

of RF2948B.

Transmit gain control output to RF2948.

RF2948 VGC receiver gain control analog output.

3-wire Bus Clock: The pin RIFSCK is the “shift clock” output. If the 3-wire bus

is enabled, address or data bits will be clocked out from the RIFSD pin with

rising edges of RIFSCK.

3-wire Bus Data: The pin RIFSD is the output “data” pin. The detail timing is on

11.3.3.

3-wire Bus Enable: The pin RFLE is an “enable” signal. It is level sensitive: If

RFLE is of LOW value, the 3-wire bus interface on the SA2400 is enabled. This

means that each rising edge on the RIFSCK pin will be taken as a shift cycle,

and address/data bits are expected on RIFSD. If RFLE is HIGH, the 3-wire bus

interface is disabled. No register settings will change regardless activity on

RIFSCK and RIFSD.

AGCSET of the Philips Chipset: On the digital output pin AGCRESET, a 0 => 1

transition clears AGCSET of SA2400 to logic 0 and SA2400 starts the AGC

cycle. At end of AGC cycle, the AGCSET of SA2400 is asserted to logic 1. Then,

AGCRESET will return to logic low.

AGCRESET of the Philips Chipset: Please refer to the AGCSET description and

Philips SA2400 datasheet.

Not used in Philips RF chipset.

Antenna Select +: The antenna selects signal changes state as the receiver

switches from antenna to antenna during the acquisition process in the antenna

diversity mode. This is a complement for ANTSEL- for differential drive of

antenna switches.

Antenna Select -: The antenna selects signal changes state as the receiver

switches from antenna to antenna during the acquisition process in the antenna

diversity mode. This is a complement for ANTSEL+ for differential drive of

antenna switches.

Transmit and Receive Switch Control: This is a complement for TRSW-.

1:TX

0:RX

8

v1.0