UPD16640CN 데이터 시트보기 (PDF) - NEC => Renesas Technology

부품명

상세내역

제조사

UPD16640CN Datasheet PDF : 16 Pages

| |||

µ PD16640C

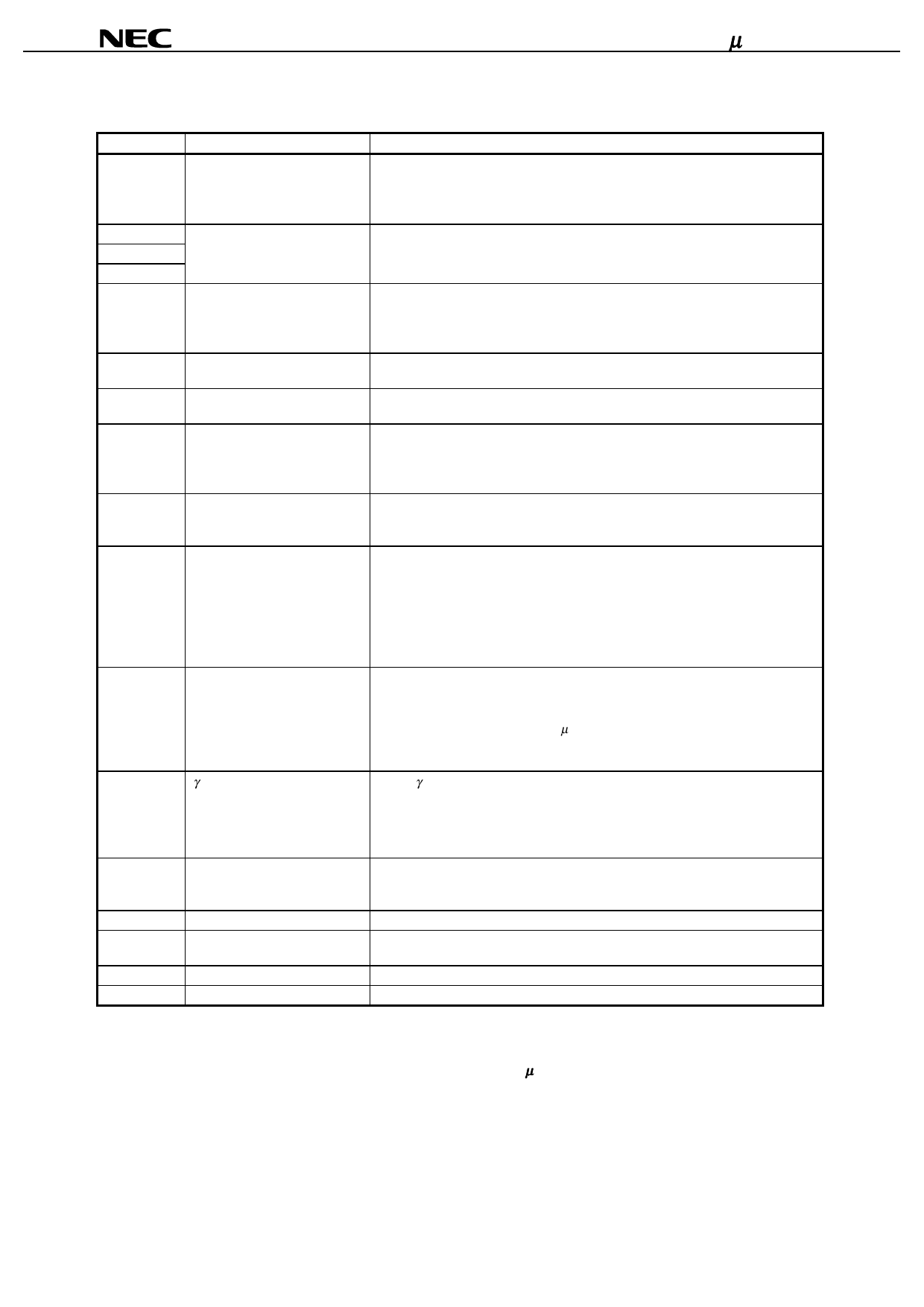

3. PIN FUNCTIONS

Pin Symbol

S1 to S309

Pin Name

Driver output

D00 to D05

D10 to D15

D20 to D25

R,/L

Display data input

Shift direction select input

STHR

STHL

Osel

Right shift start pulse I/O

Left shift start pulse I/O

Number of output selection

Vsel

Driver voltage selection

CLK

Shift clock input

STB

Latch input

V0 to V10

γ-corrected power supply

INV

VDD1

VDD2

VSS1

VSS2

Data inversion input

Logic circuit power supply

Driver circuit power supply

Logic ground

Driver ground

Description

Output 64 gray scale analog voltages converted from digital signals.

Osel = H : 300 outputs (S1 - S150, S160 - S309)

Osel = L : 309 outputs (S1 - S309)

Output pins S151 to S159 are invalid in 300-output mode.

Inputs 18-bit-wide display gray scale data (6 bits) x 3 dots (RGB).

DX0 : LSB, DX5 : MSB

This pin inputs/outputs start pulses in cascade mode.

Shift direction of shift register is as follows:

R,/L = H : STHR input, S1 → S309, STHL output

R,/L = L : STHL input, S309 → S1, STHR output

R,/L = H : Inputs start pulse

R,/L = L : Outputs start pulse

R,/L = H : Outputs start pulse

R,/L = L : Inputs start pulse

Selects number of outputs. This pin is internally pulled up by VDD1 power

supply.

Osel = H : 300 outputs

Osel = L : 309 outputs

Selects driver voltage. This pin is internally pulled up by VDD2 power supply.

Vsel = H : 300 outputs

Vsel = L : 309 outputs

Inputs shift clock to shift register. Display data is loaded to data register at

rising edge of this pin.

When Osel = H, start pulse output goes high at rising edge of 100th clock after

start pulse has been input, and serves as start pulse to driver in next stage.

When Osel = L, start pulse output goes high at rising edge of 103rd clock after

start pulse has been input, and serves as start pulse to driver in next stage.

103rd clock of driver in first stage serves as start pulse of driver in next stage.

Contents of data register are latched at rising edge, transferred to D/A

converter, and output as analog voltage corresponding to display data.

Contents of internal shift register are cleared after STB has been input. One

pulse of this signal is input when µPD16640C is started, and then device

operates normally. For STB input timing, refer to 8. SWITCHING

CHARACTERISTIC WAVEFORM.

Inputs γ-corrected power from external source.

VSS2+0.1 V ≤ V10 ≤ V9 ≤ V8 ≤ V7 ≤ V6 ≤ V5 ≤ V4 ≤ V3 ≤ V2 ≤ V1 ≤ V0 ≤VDD2−0.1 V

or

VSS2+0.1 V ≤ V0 ≤ V1 ≤ V2 ≤ V3 ≤ V4 ≤ V5 ≤ V6 ≤ V7 ≤ V8 ≤ V9 ≤ V10 ≤VDD2−0.1 V

Maintain gray scale power supply during gray scale voltage output.

Input data can be inverted when display data is loaded.

INV = H : Inverts and loads input data.

INV = L : Does not invert input data.

3.3 V ± 0.3 V

Vsel = H : VDD2 = 3.3 V ± 0.3 V

Vsel = L : VDD2 = 5.0 V ± 0.5 V

Ground

Ground

Caution Be sure to turn on power in the order VDD1, logic input, VDD2, and gray scale power (V0 to V10),

and turn off power in the reverse order, to prevent the µ PD16640C from being damaged by latchup.

Be sure to observe this power sequence even during a transition period.

4

Data Sheet S11269EJ1V1DS00