VDD18SCTA 데이터 시트보기 (PDF) - AnaSem Semiconductors

부품명

상세내역

제조사

VDD18SCTA

VDD18SCTA Datasheet PDF : 22 Pages

| |||

Rev. C09-09

低电压, 低功耗, ±1% 高精度电压检测内置延迟电路 CMOS 电压检测器

VDD 系列

工作原理解说

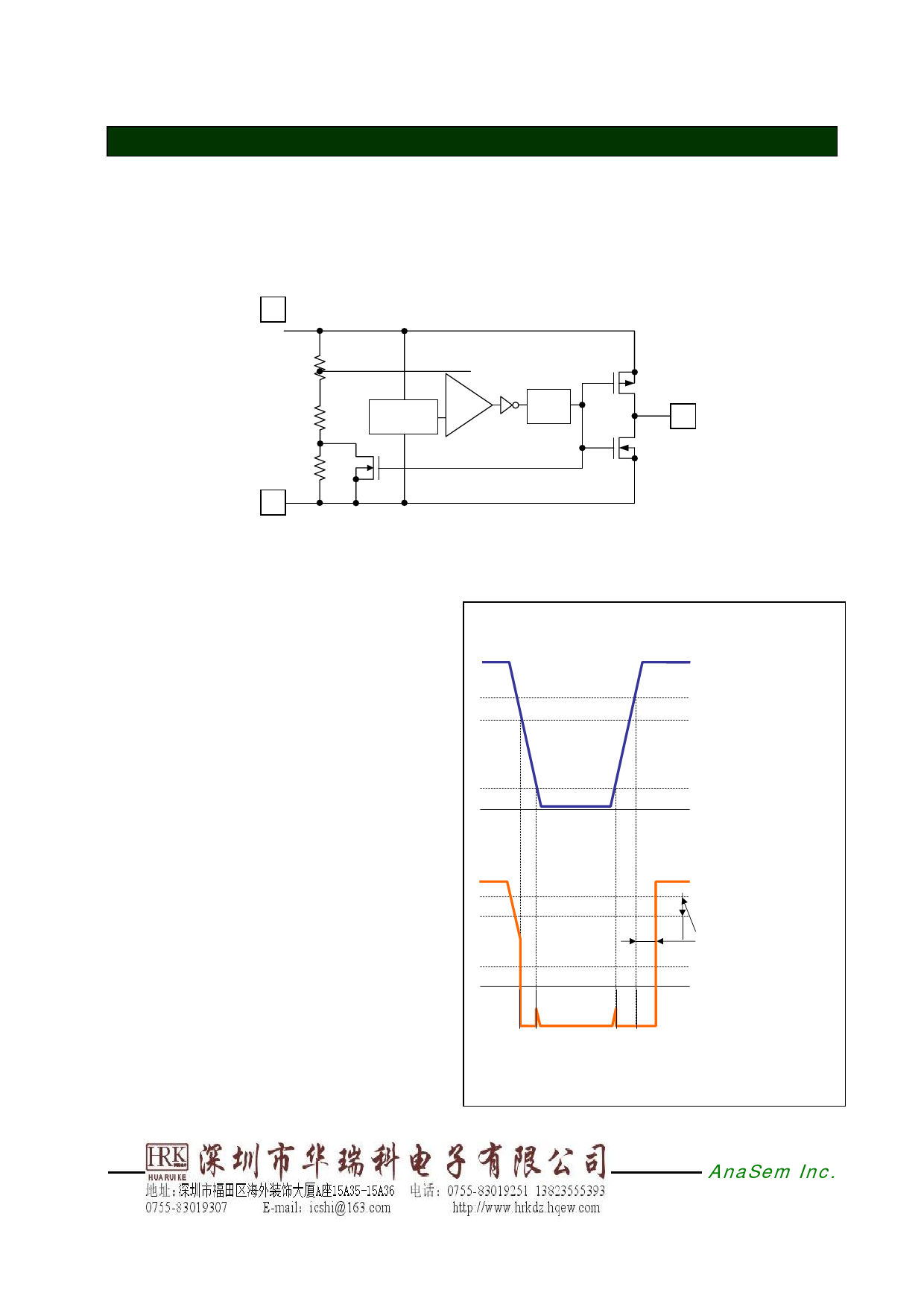

z 一般运作 (CMOS式输出)

请产考以下CMOS式输出的VDD系列电路图 ;

VIN

+

Voltage _

Reference

Delay

Circuit

P-ch

VOUT

N-ch

Vss

A. 当输入电压(VIN)高于释放电压(VREL), 输入电压(VIN)会由输出端提供,因此时电路内的N-沟道 三极管

为OFF的状态而P-沟道三极管会成ON的状态。此外, 如输入电压保持在高于设定的检测电压(VDET)时

输出电压会保持与输入电压(VIN)相等。

B. 当输入电压(VIN)下降至低于设定的检测电压

(VDET), 电路内的N-沟道三极管为ON状态,

而 P-沟道三极管会成为OFF。此外,此情况

下电压输出(VOUT)与地电压(VSS)相等。

C. 当输入电压(VIN)下降至低于最低工作电压,

电压输出(VOUT)会成不稳定状况, 或当电压输

出被拉至输入电压时电压输出(VOUT)水平会

达至输入电压(VIN)水平。

D. 当输入电压(VIN)上升至高于最低工作电压时,

虽然输入电压(VIN)升高于检测电压(VDET),

在不超于释放电压(VREL)的情况下,地电压

(VSS)会保持原来的水平。

E. 随着延迟时间, 当输入电压(VIN)升至超于释

放电压(VREL)时,内置的N-沟道三极管会成

OFF状态,而P-沟道三极管会成ON状态。此

外, 在此情况下输出电压(VOUT)与输入电压

(VIN)相等. 此释放电压(VREL)与检测电压(VD

ET)的相差乃滯後现象范围(VHYS)。

[ 运作时间表 ]

输入电压 (VIN)

释放电压 (VREL)

检测电压 (VDET)

最低工作电压

地电压 (VSS)

AB C

DE

输出电压 (VOUT)

释放电压 (VREL)

Detection voltage (VDET)

滯後现象范围(VHYS)

延迟时间 (TDLY)

最低工作电压

地电压 (VSS)

AnaSem Inc.

7

.......... Future of the analog world