WED3C7558M-XBX 데이터 시트보기 (PDF) - White Electronic Designs Corporation

부품명

상세내역

제조사

WED3C7558M-XBX Datasheet PDF : 13 Pages

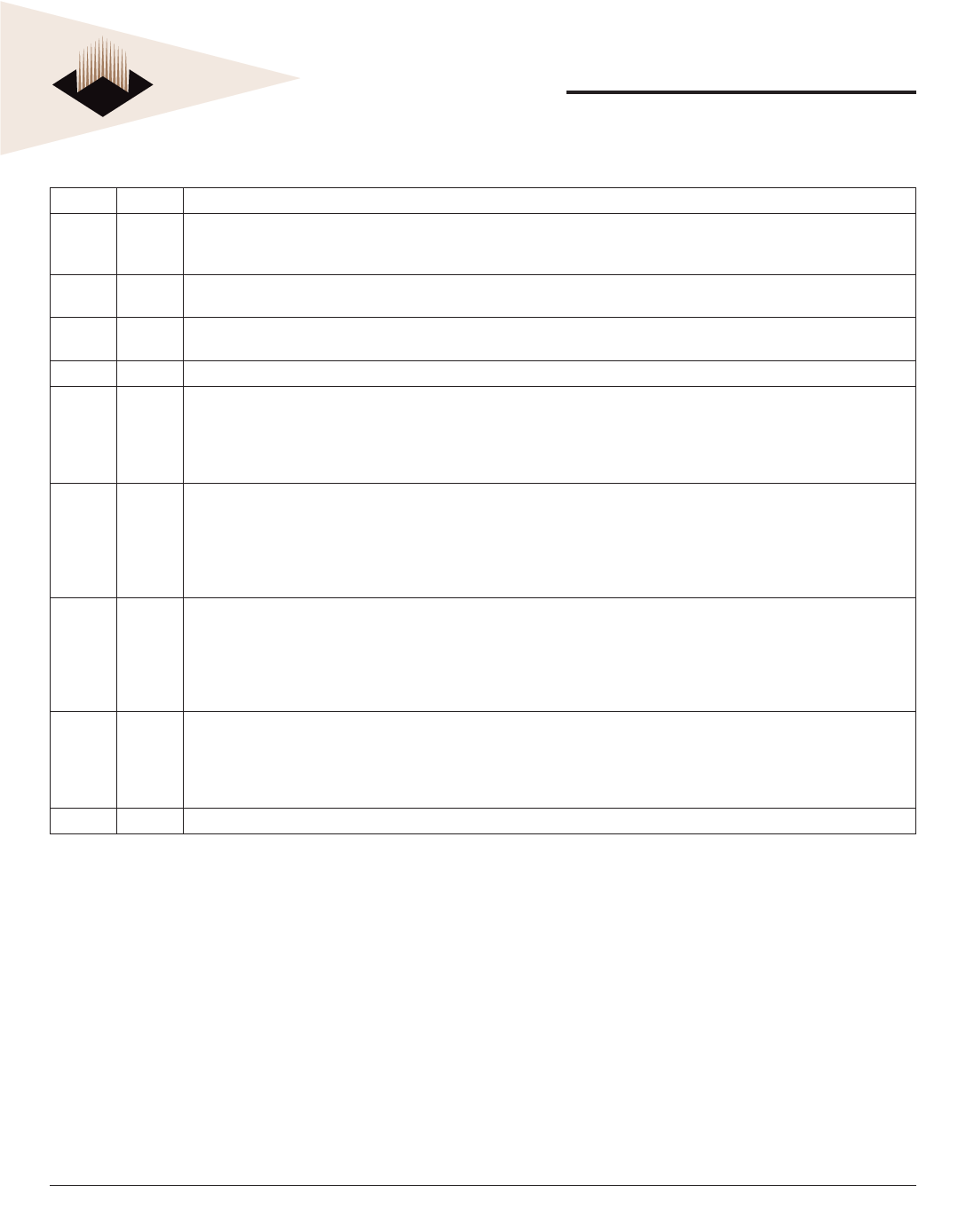

| |||

White Electronic Designs

WED3C7558M-XBX

Bit

16

17

18

19-20

21

22

23

24–30

31

Name

L2SL

L2DF

L2BYP

—

L2IO

L2CS

L2DRO

L2CTR

L2IP

TABLE 1: L2CR BIT SETTINGS

Function

L2 DLL slow. Setting L2SL increases the delay of each tap of the DLL delay line. It is intended to increase the delay through the DLL

to accommodate slower L2 RAM bus frequencies.

0: Setting for WED3C7558M-XBX because L2 RAM interface is operated above 100 MHz.

L2 differential clock. This mode supports the differential clock requirements of late-write SRAMs.

0: Setting for WED3C7558M-XBX because late-write SRAMs are not used.

L2 DLL bypass is reserved.

0: Setting for WED3C7558M-XBX

Reserved. These bits are implemented but not used; keep at 0 for future compatibility.

L2 Instruction-only. Setting this bit enables instruction-only operation in the L2 cache. For this operation, data transactions from the L1

data cache already cached in the L2 cache can hit in the L2 (including writes), but new data transactions (transactions that miss in the

L2) from the L1 data cashe are treated as cache-inhibited (bypass L2 cache, no L2 checking done). When both L2DO and L2IO are

set, the L2 cache is effectively locked (cache misses do not cause new entries to be allocated but write hits use the L2). Note that this

bit can be programmed dynamically.

L2 Clock Stop. Setting this bit causes the L2 clocks to the SRAMs to automatically stop whenever the MPC755 enters nap or sleep

modes, and automatically restart when exiting those modes (including for snooping during nap mode). It operates by asynchronously

gating off the L2CLK_OUT [A:B] signals while in nap or sleep mode. The L2SYNC_OUT/SYNC_IN path remains in operation, keeping

the DLL synchronized. This bit is provided as a power-saving alternative to the L2CTL bit and its corresponding ZZ pin, which may not

be useful for dynamic stopping/restarting of the L2 interface from nap and sleep modes due to the relatively long recovery time from

ZZ negation that the SRAM requires.

L2 DLL rollover. Setting this bit enables a potential rollover (or actual rollover) condition of the DLL to cause a checkstop for the

processor. A potential rollover condition occurs when the DLL is selecting the last tap of the delay line, and thus may risk rolling over

to the first tap with one adjustment while in the process of keeping synchronized. Such a condition is improper operation for the DLL,

and, while this condition is not expected, it allows detection for added security. This bit can be set when the DLL is first enabled (set

with the L2CLK bits) to detect rollover during initial synchronization. It could also be set when the L2 cache is enabled (with L2E bit)

after the DLL has achieved its initial lock.

L2 DLL counter (read-only). These bits indicate the current value of the DLL counter (0 to 127). They are asynchronously read when

the L2CR is read, and as such should be read at least twice with the same value in case the value is asynchronously caught in

transition. These bits are intended to provide observability of where in the 128-bit delay chain the DLL is at any given time. Generally,

the DLL operation should be considered at risk if it is found to be within a couple of taps of its beginning or end point (tap 0 or tap

128).

L2 global invalidate in progress (read only)—See the Motorola user’s manual for L2 Invalidation procedure.

August 2002

Rev. 7

10

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com