MC100ELT21 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

제조사

MC100ELT21 Datasheet PDF : 3 Pages

| |||

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Differential PECL to TTL

Translator

The MC10ELT/100ELT21 is a differential PECL to TTL translator.

Because PECL (Positive ECL) levels are used only +5V and ground are

required. The small outline 8-lead SOIC package and the single gate of

the ELT21 makes it ideal for those applications where space,

performance and low power are at a premium. Because the mature

MOSAIC 1.5 process is used, low cost can be added to the list of

features.

The VBB output allows the ELT21 to also be used in a single-ended

input mode. In this mode the VBB output is tied to the IN input for a

non-inverting buffer or the IN input for an inverting buffer. If used the VBB

pin should be bypassed to ground via a 0.01µF capacitor.

The ELT21 is available in both ECL standards: the 10ELT is compatible

with positive MECL 10H logic levels while the 100ELT is compatible with

positive ECL 100K logic levels.

• 3.5ns Typical Propagation Delay

• Differential PECL Inputs

• Small Outline SOIC Package

• 24mA TTL Output

• Flow Through Pinouts

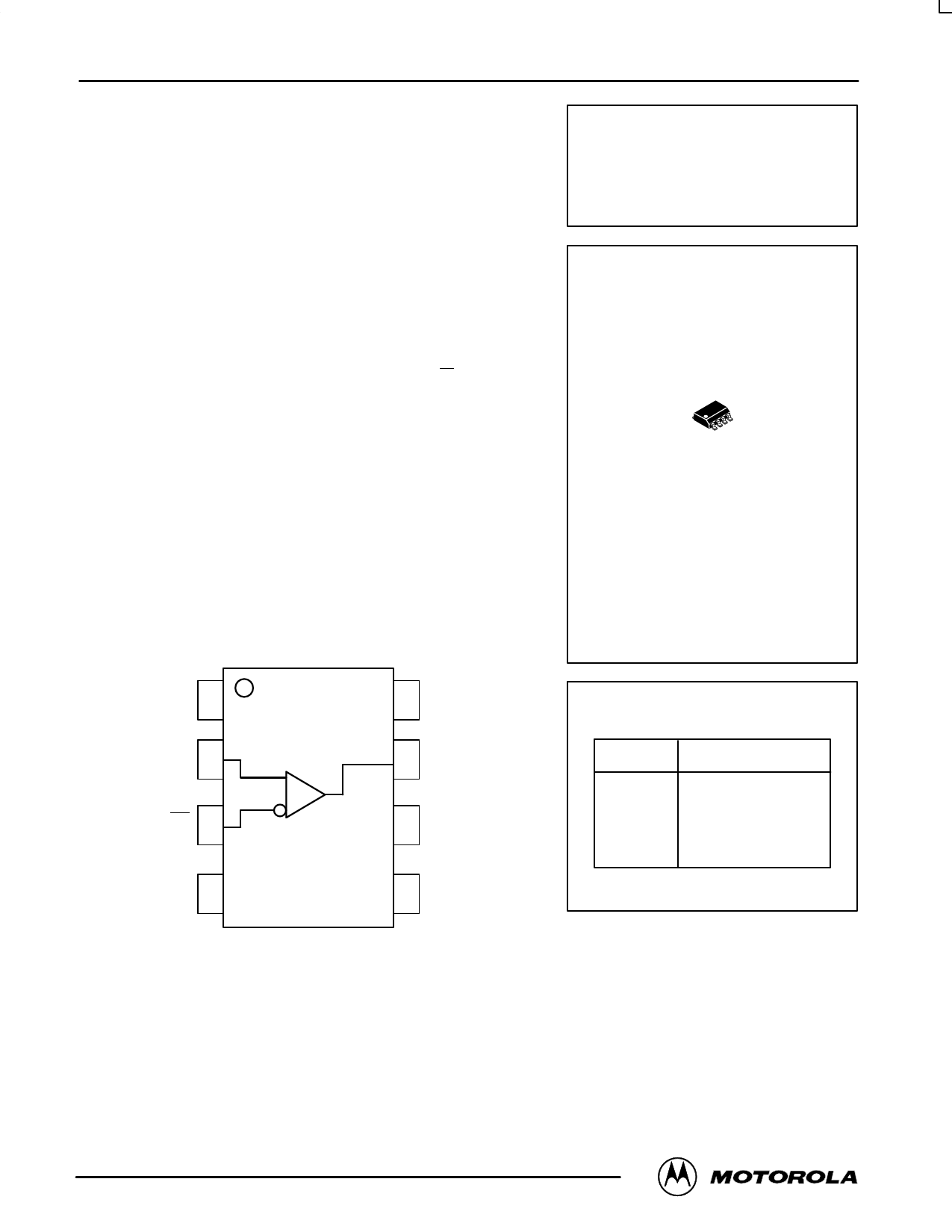

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

NC 1

D0 2

PECL

D0 3

8 VCC

TTL 7 Q0

6 NC

VBB 4

5 GND

MC10ELT21

MC100ELT21

8

1

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

PIN DESCRIPTION

PIN

Q

D

VCC

VBB

GND

FUNCTION

TTL Output

Diff PECL Inputs

+5.0V Supply

Reference Output

Ground

7/96

© Motorola, Inc. 1996

3–1

REV 3