F25L004A-50DG 데이터 시트보기 (PDF) - [Elite Semiconductor Memory Technology Inc.

부품명

상세내역

제조사

F25L004A-50DG Datasheet PDF : 30 Pages

| |||

ESMT

F25L004A

Fast-Read (50 MHz ; 100 MHz)

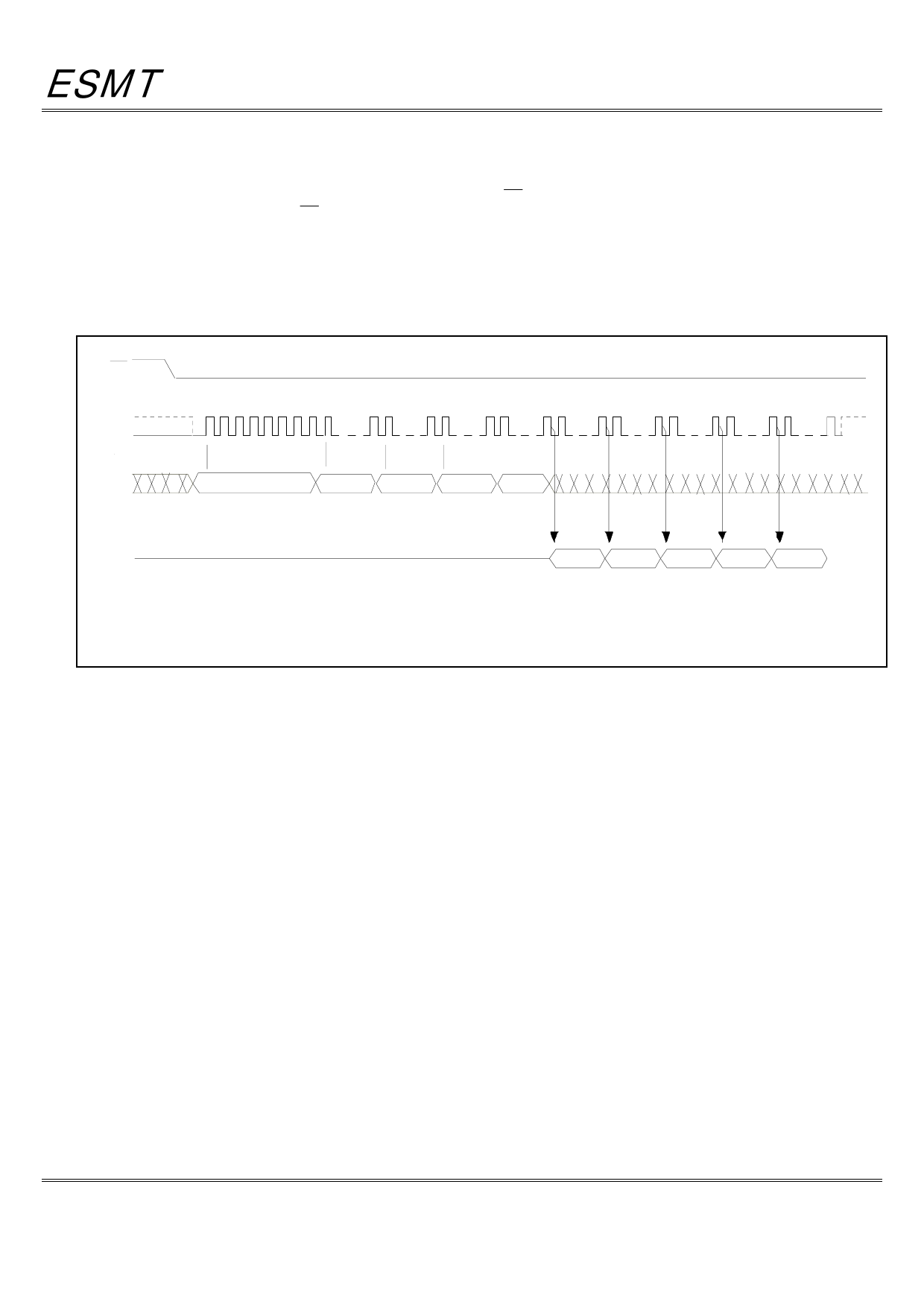

The High-Speed-Read instruction supporting up to 100 MHz is

initiated by executing an 8-bit command, 0BH, followed by

address bits [A23-A0] and a dummy byte. CE must remain active

low for the duration of the High-Speed-Read cycle. See Figure 3

for the High-Speed-Read sequence.

Following a dummy byte (8 clocks input dummy cycle), the

High-Speed-Read instruction outputs the data starting from the

specified address location. The data output stream is continuous

through all addresses until terminated by a low to high transition

on CE . The internal address pointer will automatically increment

until the highest memory address is reached. Once the highest

memory address is reached, the address pointer will

automatically increment to the beginning (wrap-around) of the

address space, i.e. for 4Mbit density, once the data from address

location 7FFFFH has been read, the next output will be from

address location 000000H.

CE

MODE3

SCK MODE0

0 12 3 45 67 8

15 16 23 24

31 32 39 40 47 48 55 56 63 64 71 72

80

SI

0B

ADD.

ADD.

A DD.

MSB

MSB

HIGH IMPENANCE

SO

Note : X = Dummy Byte : 8 Clocks Input Dummy (VIL or VIH)

X

N

D OU T

MSB

N+1

DOUT

N+2

DOUT

N+3

D OU T

N+4

D OU T

Figure 3 : HIGH-SPEED-READ SEQUENCE

Elite Semiconductor Memory Technology Inc.

Publication Date: Jan. 2009

Revision: 1.6

9/30