F25L32PA-86PAG 데이터 시트보기 (PDF) - [Elite Semiconductor Memory Technology Inc.

부품명

상세내역

제조사

F25L32PA-86PAG

F25L32PA-86PAG Datasheet PDF : 36 Pages

| |||

ESMT

TOP

Protection Level

0

Upper 1/64

Upper 1/32

Upper 1/16

Upper 1/8

Upper 1/4

Upper 1/2

All Blocks

F25L32PA

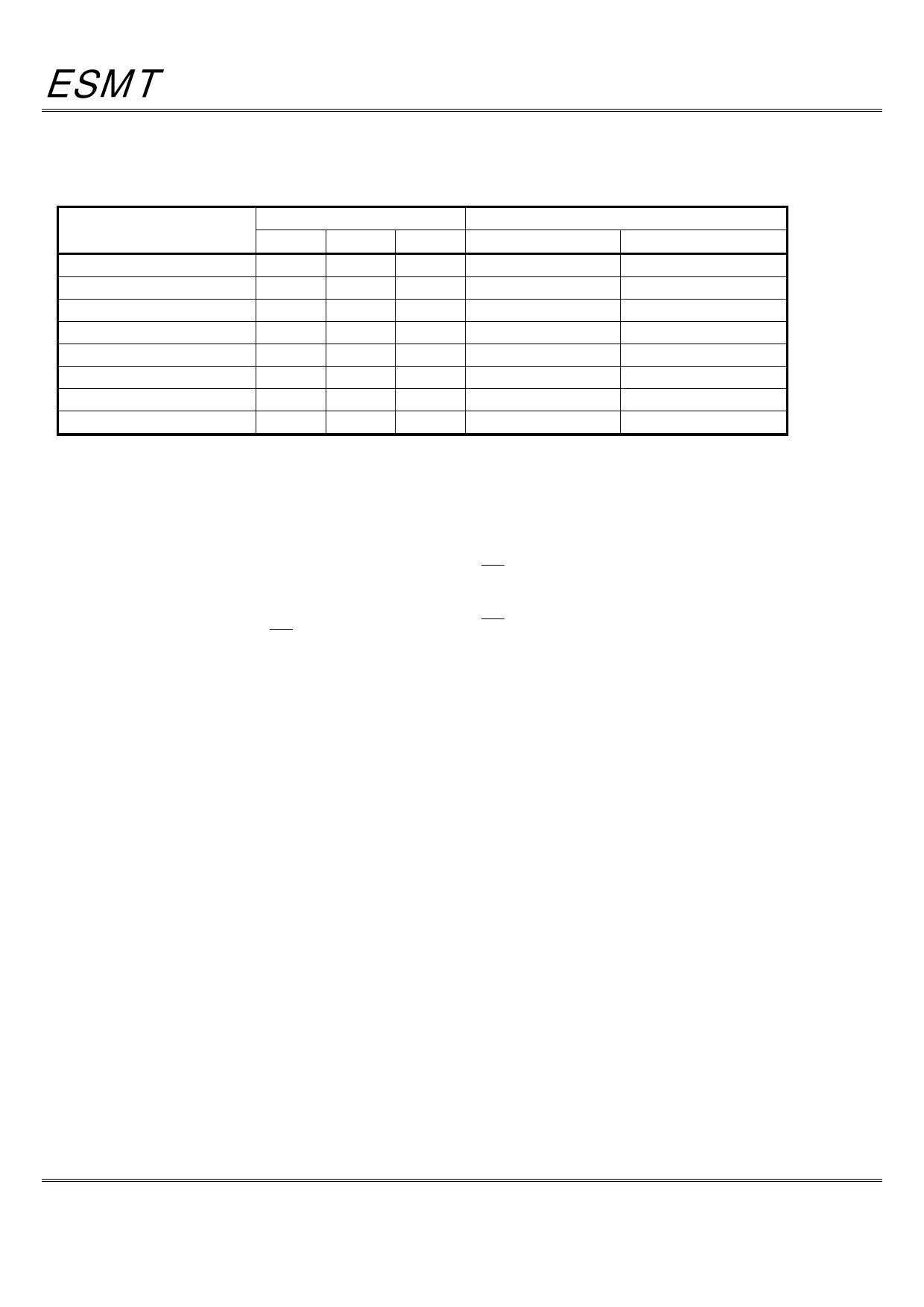

Table 3: F25L32PA Block Protection Table

Status Register Bit

BP2

BP1

BP0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Protected Memory Area

Block Range

Address Range

None

None

Block 63

3F0000H –3FFFFFH

Block 62~63

3E0000H –3FFFFFH

Block 60~63

3C0000H –3FFFFFH

Block 56~63

380000H –3FFFFFH

Block 48~63

300000H –3FFFFFH

Block 32~63

200000H –3FFFFFH

Block 0~63

000000H –3FFFFFH

Block Protection (BP2, BP1, BP0)

The Block-Protection (BP2, BP1, BP0) bits define the size of the

memory area, as defined in Table 3, to be software protected

against any memory Write (Program or Erase) operations. The

Write Status Register (WRSR) instruction is used to program the

BP2, BP1, BP0 bits as long as WP is high or the Block-

Protection-Look (BPL) bit is 0. Chip Erase can only be executed if

Block-Protection bits are all 0. After power-up, BP2, BP1 and BP0

are set to1.

Block Protection Lock-Down (BPL)

WP pin driven low (VIL), enables the Block-Protection-

Lock-Down (BPL) bit. When BPL is set to 1, it prevents any

further alteration of the BPL, BP2, BP1, and BP0 bits. When the

WP pin is driven high (VIH), the BPL bit has no effect and its

value is “Don’t Care”. After power-up, the BPL bit is reset to 0.

Elite Semiconductor Memory Technology Inc.

Publication Date: Mar. 2009

Revision: 1.0

10/36