ISP1181 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

제조사

ISP1181 Datasheet PDF : 69 Pages

| |||

Philips Semiconductors

ISP1181

Full-speed USB interface

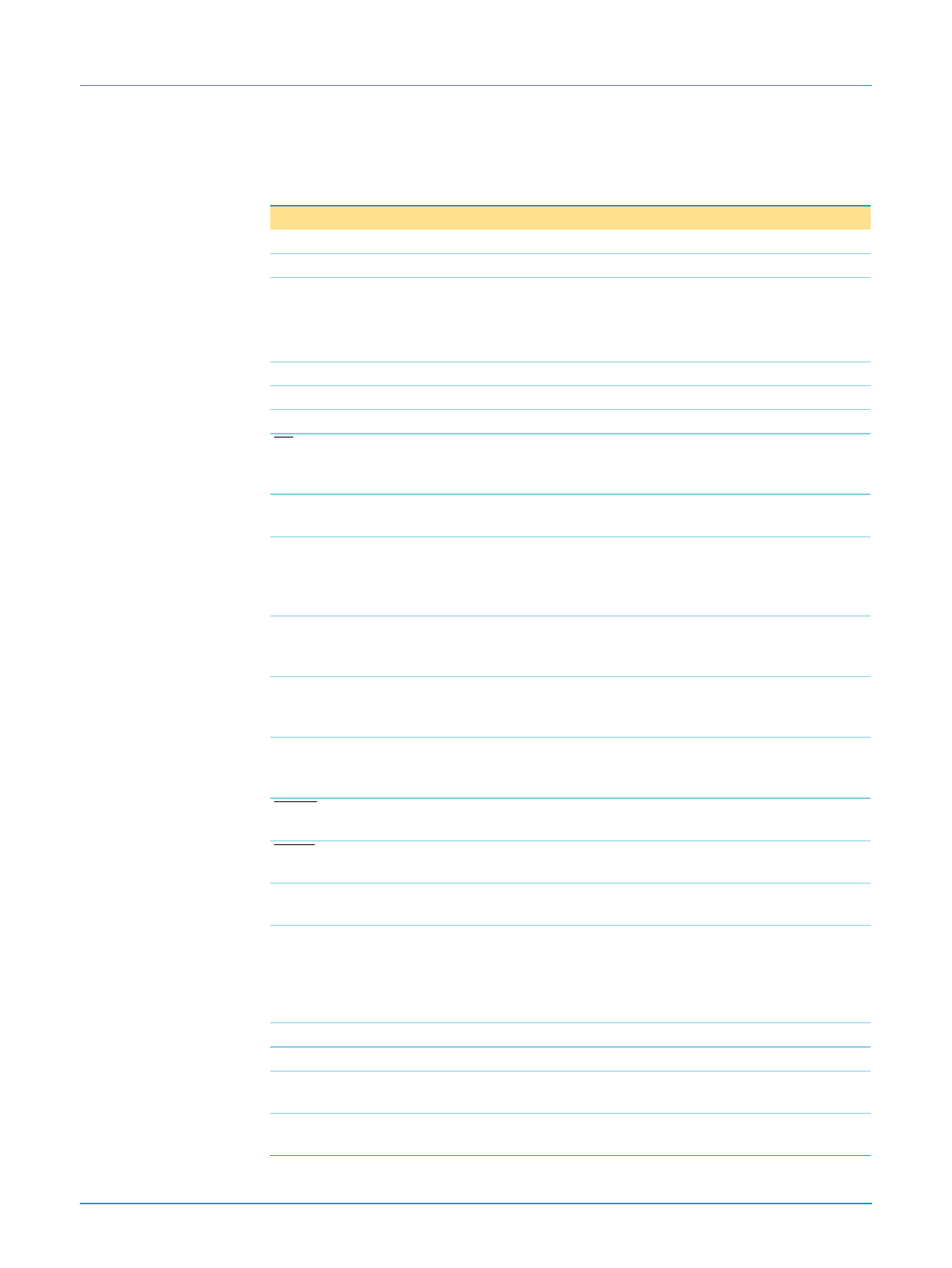

6.2 Pin description

Table 2: Pin description for TSSOP48

Symbol [1]

Pin Type Description

VCC(5.0)

REGGND

1

-

2

-

supply voltage (3.0 to 5.5 V)

voltage regulator ground supply

Vreg(3.3)

3

-

regulated supply voltage (3.3 V ± 10%) from internal

regulator; used to connect decoupling capacitor and pull-up

resistor on D+ line;

Remark: Cannot be used to supply external devices.

D−

4

AI/O USB D− connection (analog)

D+

5

AI/O USB D+ connection (analog)

VBUS

GL

6

I

VBUS sensing input

7

O

GoodLink LED indicator output (open-drain, 8 mA); the LED

is default ON, blinks OFF upon USB traffic; to connect an

LED use a 330 Ω series resistor;

WAKEUP

8

I

wake-up input (edge triggered, LOW to HIGH); generates a

remote wake-up from ‘suspend’ state

SUSPEND 9

O

‘suspend’ state indicator output (4 mA); used as power switch

control output (active LOW) for powered-off application or as

resume signal to the CPU (active HIGH) for powered-on

application

EOT

10 I

End-Of-Transfer input (programmable polarity, see Table 23);

used by the DMA controller to force the end of a DMA transfer

by the ISP1181

DREQ

11 O

DMA request output (4 mA; programmable polarity, see

Table 23); signals to the DMA controller that the ISP1181

wants to start a DMA transfer

DACK

12 I

DMA acknowledge input (programmable polarity, see

Table 23); used by the DMA controller to signal the start of a

DMA transfer requested by the ISP1181

SDWR

13 I

DMA write strobe input; used only in bus configuration

mode 1 (separate PIO and DMA ports)

SDRD

14 I

DMA read strobe input; used only in bus configuration

mode 1 (separate PIO and DMA ports)

INT

15 O

interrupt output; programmable polarity (active HIGH or LOW)

and signalling (level or pulse); see Table 23

READY

16 O

I/O ready output; a LOW level indicates that ISP1181 is

processing a previous command or data and is not ready for

the next PIO command or data transfer; a HIGH level signals

that ISP1181 will complete a PIO data transfer; applies only

to a PIO port or a PIO port shared with a DMA port

BUS_CONF1 17 I

bus configuration selector; see Table 3

BUS_CONF0 18 I

bus configuration selector; see Table 3

DATA15

19 I/O bit 15 of D[15:0]; bi-directional data line (slew-rate controlled

output, 4 mA)

DATA14

20 I/O bit 14 of D[15:0]; bi-directional data line (slew-rate controlled

output, 4 mA)

9397 750 06896

Objective specification

Rev. 01 — 13 March 2000

© Philips Electronics N.V. 2000. All rights reserved.

5 of 69