M12L16161A-7TIG 데이터 시트보기 (PDF) - [Elite Semiconductor Memory Technology Inc.

부품명

상세내역

제조사

M12L16161A-7TIG Datasheet PDF : 29 Pages

| |||

ESMT

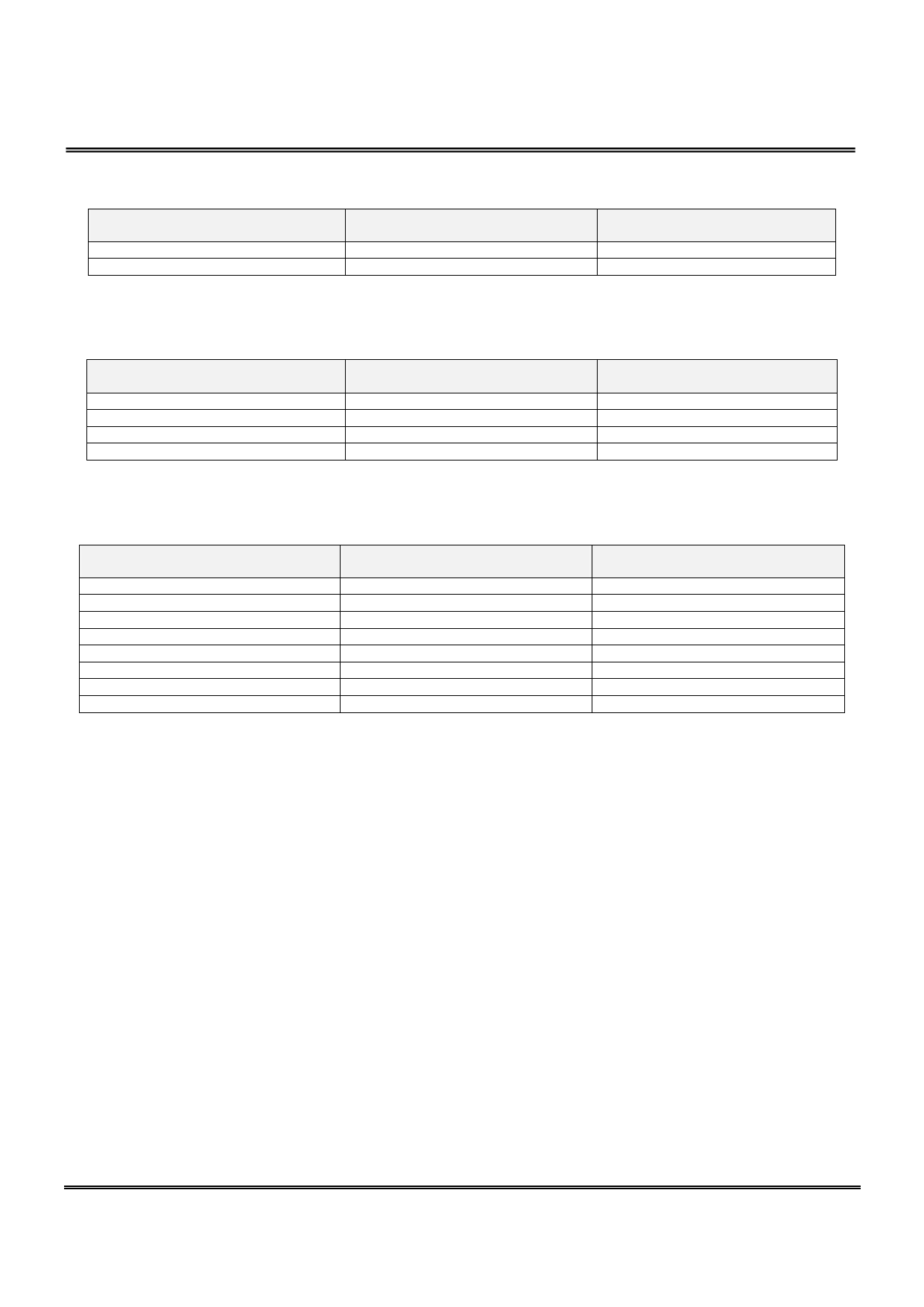

Burst Length and Sequence

(Burst of Two)

Starting Address

(column address A0 binary)

0

1

M12L16161A

Operation temperature condition -40℃~85℃

Sequential Addressing

Sequence (decimal)

0,1

1,0

Interleave Addressing

Sequence (decimal)

0,1

1,0

(Burst of Four)

Starting Address

(column address A1-A0, binary)

00

01

10

11

Sequential Addressing

Sequence (decimal)

0,1,2,3

1,2,3,0

2,3,0,1

3,0,1,2

Interleave Addressing

Sequence (decimal)

0,1,2,3

1,0,3,2

2,3,0,1

3,2,1,0

(Burst of Eight)

Starting Address

(column address A2-A0, binary)

000

001

010

0 11

100

101

11 0

111

Sequential Addressing

Sequence (decimal)

0,1,2,3,4,5,6,7

1,2,3,4,5,6,7,0

2,3,4,5,6,7,0,1

3,4,5,6,7,0,1,2

4,5,6,7,0,1,2,3

5,6,7,0,1,2,3,4

6,7,0,1,2,3,4,5

7,0,1,2,3,4,5,6

Interleave Addressing

Sequence (decimal)

0,1,2,3,4,5,6,7

1,0,3,2,5,4,7,6

2,3,0,1,6,7,4,5

3,2,1,0,7,6,5,4

4,5,6,7,0,1,2,3

5,4,7,6,1,0,3,2

6,7,4,5,2,3,0,1

7,6,5,4,3,2,1,0

Full page burst is an extension of the above tables of Sequential Addressing, with the length being 256 for 1Mx16 divice.

POWER UP SEQUENCE

1.Apply power and start clock, attempt to maintain CKE= “H”, L(U)DQM = “H” and the other pin are NOP condition at the inputs.

2.Maintain stable power, stable clock and NOP input condition for a minimum of 200us.

3.Issue precharge commands for all banks of the devices.

4.Issue 2 or more auto-refresh commands.

5.Issue mode register set command to initialize the mode register.

Cf.)Sequence of 4 & 5 is regardless of the order.

Elite Semiconductor Memory Technology Inc.

Publication Date : May. 2007

Revision : 1.1

9/29