NTE7134 데이터 시트보기 (PDF) - NTE Electronics

부품명

상세내역

제조사

NTE7134 Datasheet PDF : 17 Pages

| |||

Functional Description (Cont’d):

Frequency–Locked Loop

The frequency–locked loop can lock the horizontal oscillator over a wide frequency range. This is

achieved by a combined search and PLL operation. The frequency range is preset by two external

resistors and the recommended ratio is

fmin

fmax

=

1

3.5

Larger ranges are possible by extended applications.

Without a horizontal sync signal the oscillator will be free–running at fmin. Any change of sync condi-

tions is detected by the internal coincidence detector. A deviation of more than 4% between horizontal

sync and oscillator frequency switches the horizontal section into search mode. This means that PLL1

control currents are switched off immediately. Then the internal frequency detector starts tuning the

oscillator. Very small DC currents at HPLL1 (Pin26) are used to perform this tuning with a well defined

change rate. When coincidence between horizontal sync and oscillator frequency is detected, the

search mode is replaced by a normal PLL operation. This operation ensures a smooth tuning and

avoids fast changes of horizontal frequency during catching.

In this concept it is not allowed to load HPLL1. The frequency dependent voltage at this pin is fed inter-

nally to HBUF (Pin27) via a sample–and–hold and buffer stage. The sample–and–hold stage re-

moves all disturbances caused by horizontal sync or composite vertical sync from the buffered volt-

age. An external resistor from HBUF to HREF defines the frequency range.

See also hints for locking procedure in Note 2 of the “Electrical Characteristics” section of this data

sheet.

PLL1 Phase Detector

The phase detector is a standard type using switched current sources. The middle of the horizontal

sync is compared with a fixed point of the oscillator sawtooth voltage. The PLL1 loop filter is connected

to HPLL (Pin26).

Horizontal Oscillator

This oscillator is a relaxation type and requires a fixed capacitor of 10nF at HCAP (Pin29). For opti-

mum jitter performance the value of 10nF must not be changed.

The maximum oscillator frequency is determined by a resistor from HREF to GND. A resistor from

HREF to HBUF defines the frequency range.

The reference current at HREF also defines the integration time constant of the vertical sync integration.

Calculation of Line Frequency Range

First the oscillator frequencies fmin and fmax have to be calculated. This is achieved by adding the

spread of the relevant components to the highest and lowest sync frequencies fS(min) and fS(max). The

oscillator is driven by the difference of the currents in RHREF and RHBUF. At the highest oscillator fre-

quency RHBUF does not contribute to the spread. The spread will increase towards lower frequencies

due to the contribution of RHBUF. It is also dependent on the ratio

fS(max)

fS(min)

The following example is a 31.45 to 64kHz application:

ns =

fS(max)

fS(min)

=

64kHz

31.45kHz

= 2.04

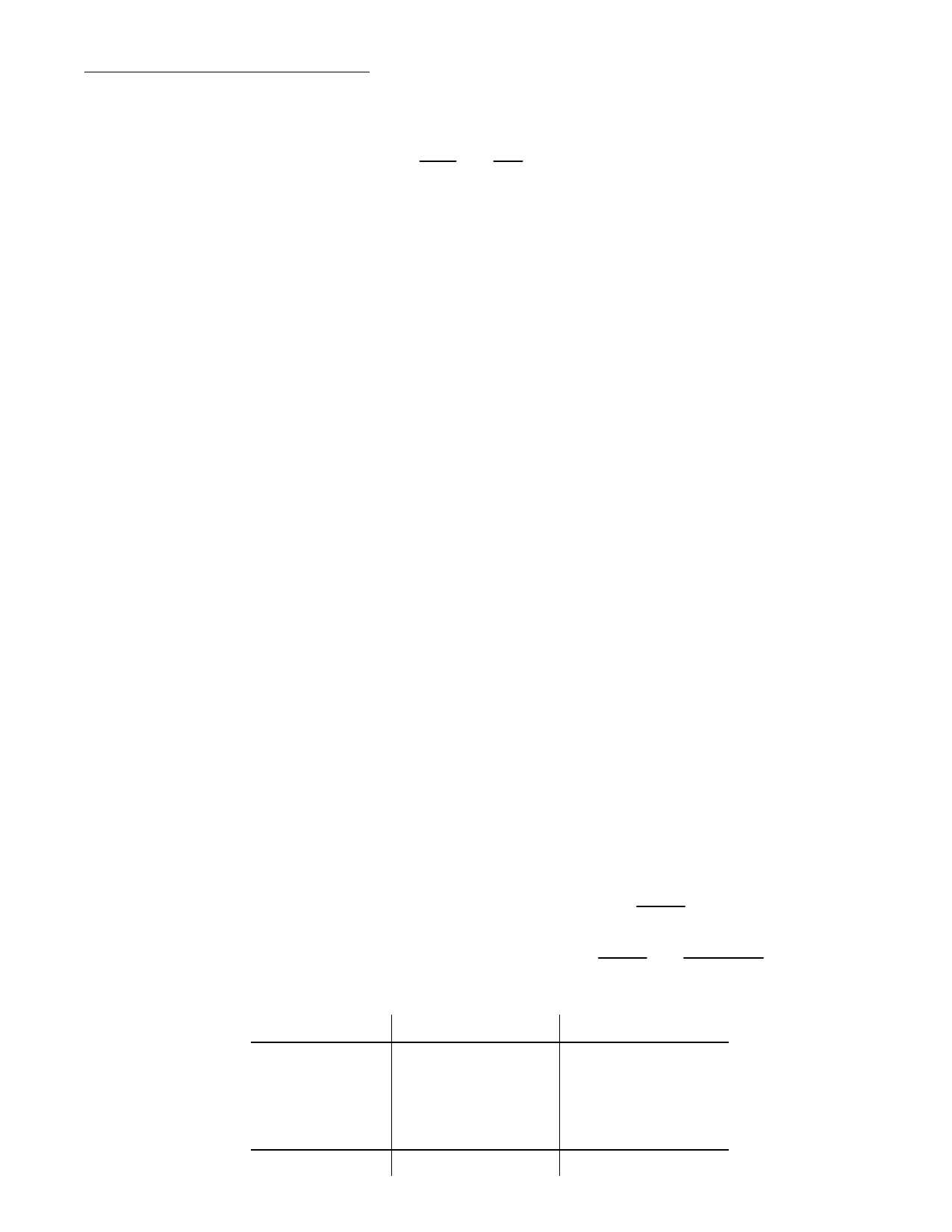

Table 1. Calculation of total spread

spread of:

for fmax

IC

3%

for fmin

3%

CHCAP

RHREF

RHREF. RHBUF

Total

2%

2%

1%

–

–

1% x (2.3 x ns –1)

6%

8,69%