ADM8693ANZ 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADM8693ANZ Datasheet PDF : 20 Pages

| |||

ADM8690/ADM8691/ADM8692/ADM8693/ADM8695

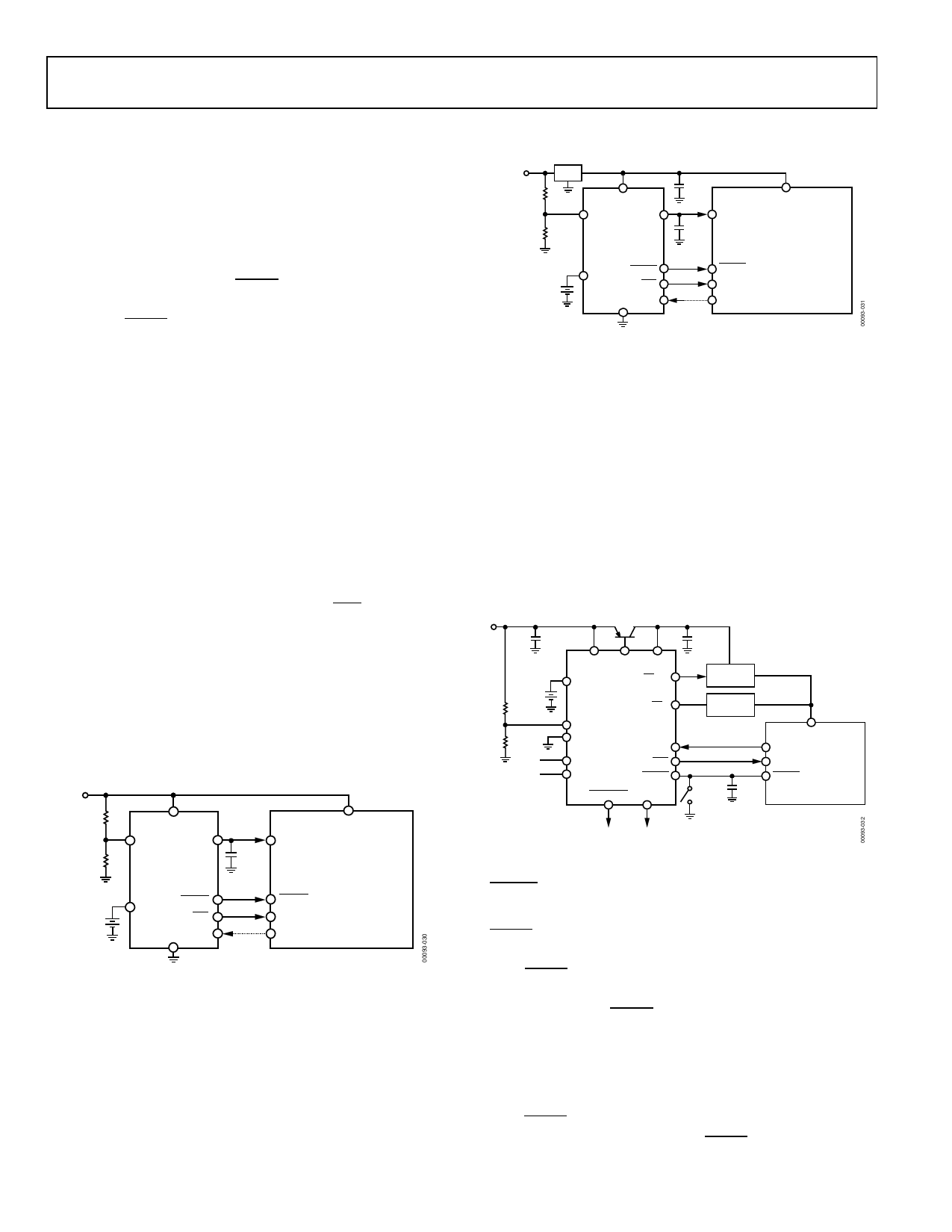

TYPICAL APPLICATIONS

ADM8690 AND ADM8692

Figure 30 shows the ADM8690/ADM8692 in a typical power

monitoring, battery backup application. VOUT powers the CMOS

RAM. Under normal operating conditions with VCC present,

VOUT is internally connected to VCC. If a power failure occurs,

VCC decays and VOUT is switched to VBATT, thereby maintaining

power for the CMOS RAM. A RESET pulse is also generated

when VCC falls below 4.65 V for the ADM8690 or 4.4 V for the

ADM8692. RESET remains low for 50 ms after VCC returns to 5 V.

INPUT

POWER

V > 8V

R1

R2

5V

7805

VCC

PFI

VOUT

ADM8690/

ADM8692

+

BATTERY

VBATT

RESET

PFO

GND WDI

0.1µF

0.1µF

POWER

CMOS RAM

POWER

MICROPROCESSOR

SYSTEM

RESET

NMI

I/O LINE

Figure 31. ADM8690/ADM8692 Typical Application Circuit B

The watchdog timer input (WDI) monitors an input/output line

from the microprocessor system. This line must be toggled once

every 1.6 seconds to verify correct software execution. Failure to

toggle the line indicates that the microprocessor system is not

correctly executing its program and can be tied up in an endless

loop. If this happens, a reset pulse is generated to initialize the

microprocessor.

If the watchdog timer is not needed, the WDI input should be

left floating.

The power-fail input, PFI, monitors the input power supply via

a resistive divider network. The voltage on the PFI input is

compared with a precision 1.3 V internal reference. If the input

voltage drops below 1.3 V, a power-fail output (PFO) signal is

generated. This warns of an impending power failure and can

be used to interrupt the processor so that the system can be shut

down in an orderly fashion. The resistors in the sensing

network are ratioed to give the desired power-fail threshold

voltage (VT).

VT = (1.3 R1/R2) + 1.3 V

R1/R2 = (VT/1.3) − 1

5V

R1

VCC

PFI

VOUT

R2

ADM8690/

ADM8692

0.1µF

POWER

CMOS RAM

POWER

MICROPROCESSOR

SYSTEM

+

BATTERY

VBATT

RESET

PFO

GND WDI

RESET

NMI

I/O LINE

Figure 30. ADM8690/ADM8692 Typical Application Circuit A

Figure 31 shows a similar application, but in this case the PFI

input monitors the unregulated input to the 7805 voltage

regulator. This gives an earlier warning of an impending power

failure. It is useful with processors operating at low speeds or

where there are a significant number of housekeeping tasks to

be completed before the power is lost.

ADM8691, ADM8693, AND ADM8695

A typical connection for the ADM8691/ADM8693/ADM8695

is shown in Figure 32. CMOS RAM is powered from VOUT.

When 5 V power is present, this is routed to VOUT. If VCC fails,

VBATT is routed to VOUT. VOUT can supply up to 100 mA from

VCC, but if more current is required, an external PNP transistor

can be added. When VCC is higher than VBATT, the BATT ON

output goes low, providing up to 25 mA of base drive for the

external transistor. A 0.1 µF capacitor is connected to VOUT to

supply the transient currents for CMOS RAM. When VCC is

lower than VBATT, an internal 20 Ω MOSFET connects the

backup battery to VOUT.

INPUT POWER

5V

0.1µF

0.1µF

3V

BATTERY

R1

R2

NC

VCC

VBATT

BATT VOUT

ON

CEOUT

ADM8691/

ADM8693/ CEIN

PFI ADM8695

GND

WD I

OSC IN

PFO

OSC SEL

RESET

LOW LINE WDO

CMOS

RAM

ADDRESS

DECODE

RESET

A0 TO 15

I/O LINE

NM I

RESET

0.1µF MICROPROCESSOR

SYSTEM

SYSTEM STATUS

INDICATORS

Figure 32. ADM8691/ADM8693/ADM8695 Typical Application

RESET OUTPUT

The internal voltage detector monitors VCC and generates a

RESET output to hold the microprocessor reset line low when

VCC is below 4.65 V (4.4 V for ADM8693). An internal timer

holds RESET low for 50 ms (200 ms for the ADM8695) after

VCC rises above 4.65 V (4.4 V for the ADM8693). This prevents

repeated toggling of RESET, even if the 5 V power drops out

and recovers with each power line cycle.

The crystal oscillator normally used to generate the clock for

microprocessors can take several milliseconds to stabilize.

Because most microprocessors need several clock cycles to

reset, RESET must be held low until the microprocessor clock

oscillator has started. The power-up RESET pulse lasts 50 ms

Rev. B | Page 16 of 20