AT24C08D 데이터 시트보기 (PDF) - Atmel Corporation

부품명

상세내역

제조사

AT24C08D Datasheet PDF : 28 Pages

| |||

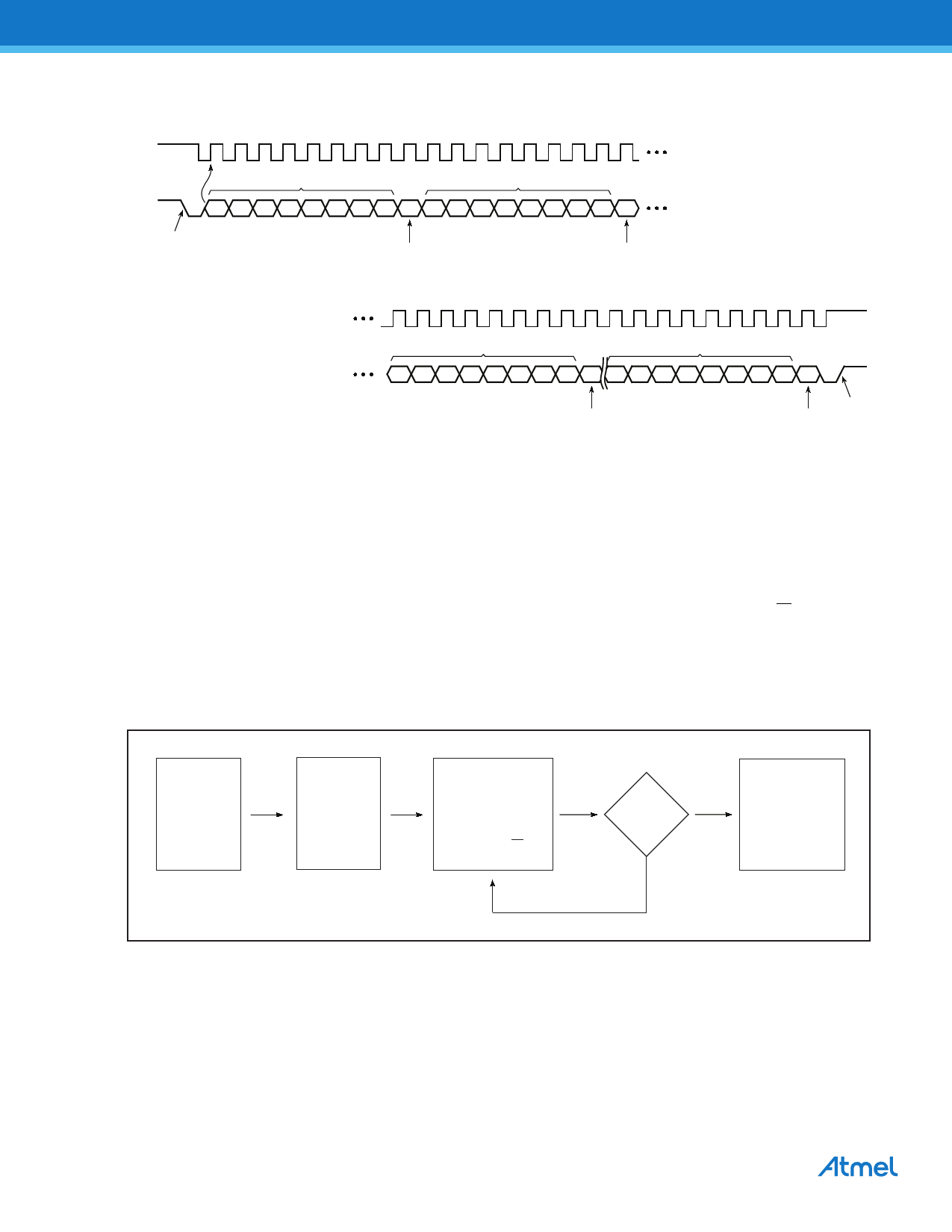

Figure 5-2. Page Write

SCL

12 3 4 567 89 12 345 67 89

SDA

Start

by

Master

Device Address Byte

Word Address Byte

1 0 1 0 A2 A9 A8 0 0 A7 A6 A5 A4 A3 A2 A1 A0 0

MSB

MSB

ACK

from

Slave

ACK

from

Slave

12 3 4 567 89 12 345 67 89

Data Word (n)

Data Word (n+x), max of 16 without rollover

D7 D6 D5 D4 D3 D2 D1 D0 0 D7 D6 D5 D4 D3 D2 D1 D0 0

MSB

MSB

ACK

from

Slave

ACK

from

Slave

Stop

by

Master

5.3 Acknowledge Polling

An Acknowledge Polling routine can be implemented to optimize time sensitive applications which would prefer not

to wait the fixed maximum write cycle time (tWR). This method allows the application to know immediately when the

Serial EEPROM write cycle has completed so a subsequent operation can be started.

Once the internally self-timed write cycle has started, an Acknowledge Polling routine can be initiated. This

involves repeatedly sending a Start condition followed by a valid Device Address byte with the R/W bit set at

Logic 0. The device will not respond with an ACK while the write cycle is ongoing. Once the internal write cycle has

completed, the EEPROM will respond with an ACK, allowing a new Read or Write operation to be immediately

initiated. A flow chart has been included below in Figure 5-3 to better illustrate this technique.

Figure 5-3. Acknowledge Polling Flow Chart

Send any

Write

protocol

Send

Stop

condition

to initiate the

write cycle

Send Start

condition followed

by a valid

Device Address

byte with R/W = 0

Did

the device

ACK?

YES

Proceed to

next Read or

Write operation

NO

5.4 Write Cycle Timing

The length of the self-timed write cycle or tWR is defined as the amount of time from the Stop condition that begins

the internal Write operation to the Start condition of the first Device Address byte sent to the AT24C08D which it

subsequently responds to with an ACK. Figure 5-4 has been included to show this measurement. During the

internally self-timed write cycle, any attempts to read from or write to the memory array will not be processed.

10 AT24C08D [DATASHEET]

Atmel-8880B-SEEPROM-AT24C08D-Datasheet_042014