AT24C08D 데이터 시트보기 (PDF) - Atmel Corporation

부품명

상세내역

제조사

AT24C08D Datasheet PDF : 28 Pages

| |||

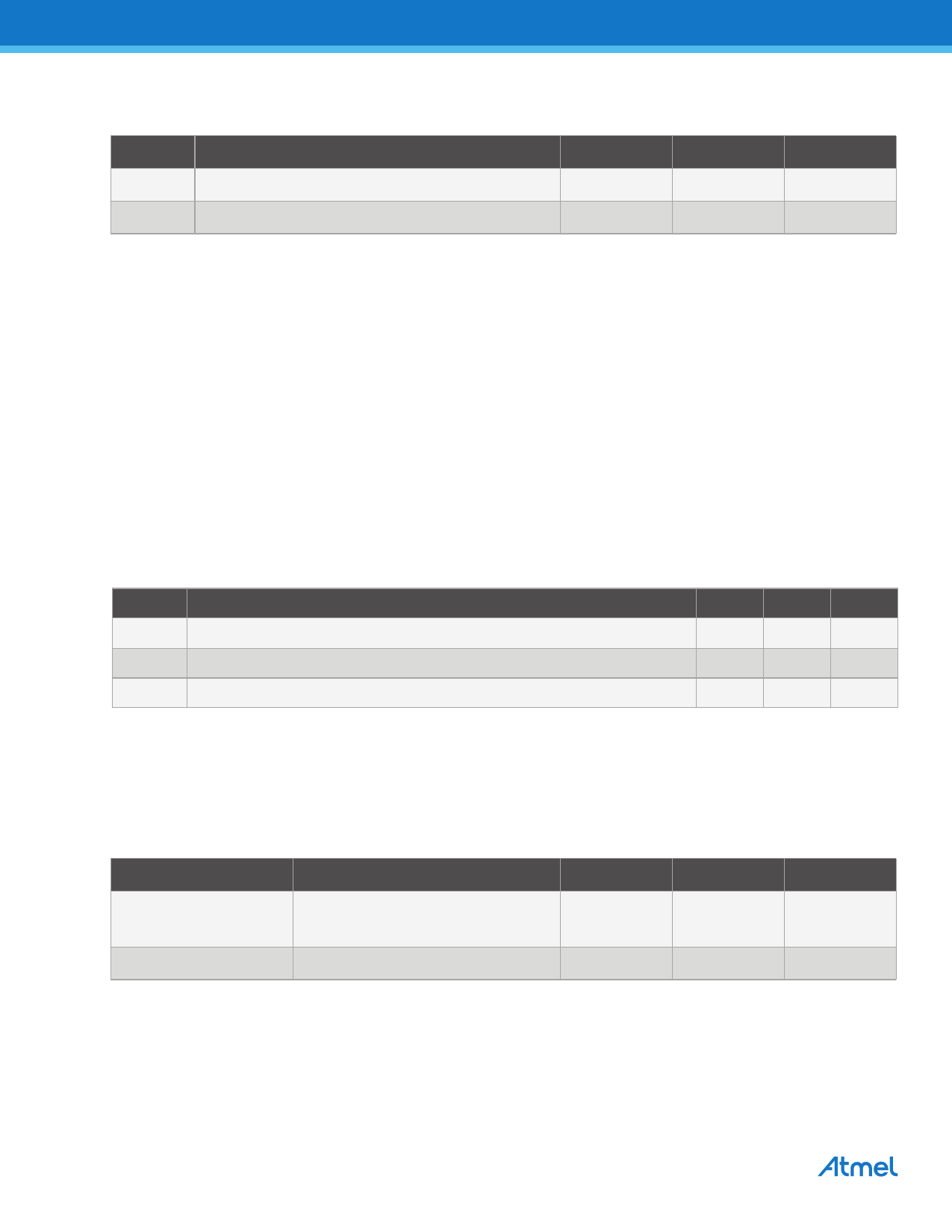

8.5 Pin Capacitance(1)

Applicable over recommended operating range from TA = 25C, f = 1.0MHz, VCC = 3.6V

Symbol Test Condition

Max

CI/O

Input/Output Capacitance (SDA)

8

CIN

Input Capacitance (A2, SCL)

6

Note: 1. This parameter is characterized but is not 100% tested in production.

Units

pF

pF

Conditions

VI/O = 0V

VIN = 0V

8.6 Power-Up Requirements and Reset Behavior

During a power-up sequence, the VCC supplied to the AT24C08D should monotonically rise from GND to the

minimum VCC level as specified in Section 8.2 with a slew rate no greater than 1V/μs.

8.6.1

Device Reset

To prevent Write operations or other spurious events from happening during a power-up sequence, the AT24C08D

includes a Power-On-Reset (POR) circuit. Upon power-up, the device will not respond to any commands until the

VCC level crosses the internal voltage threshold (VPOR) that brings the device out of reset and into standby mode.

The system designer must ensure the instructions are not sent to the device until the VCC supply has reached a

stable value greater than or equal to the minimum VCC level. Additionally, once the VCC is greater than or equal to

the minimum VCC level, the bus Master must wait at least tPUP before sending the first command to the device. See

Table 8-1 for the values associated with these power-up parameters.

Table 8-1. Power-up Conditions

Symbol Parameter

Min

Max Units

tPUP

VPOR

tPOFF

Time required after VCC is stable before the device can accept commands.

Power-On Reset Threshold Voltage

Minimum time at VCC = 0V between power cycles.

100

μs

1.5

V

1

ms

If an event occurs in the system where the VCC level supplied to the AT24C08D drops below the maximum VPOR

level specified, it is recommended that a full power cycle sequence be performed by first driving the VCC pin to

GND waiting at least the minimum tPOFF time, and then performing a new power-up sequence in compliance with

the requirements defined in this section.

8.7 EEPROM Cell Performance Characteristics

Operation

Test Condition

Min

Max

Units

Write Endurance(1)

Data Retention(2)

TA = 25°C, VCC(min)< VCC < VCC(max)

Byte or Page Write Mode

TA = 55°C, VCC(min)< VCC < VCC(max)

1,000,000

100

—

Write Cycles

—

Years

Notes: 1. Write endurance performance is determined through characterization and the qualification process.

2. The data retention capability is determined through qualification and is checked on each device in production.

16 AT24C08D [DATASHEET]

Atmel-8880B-SEEPROM-AT24C08D-Datasheet_042014