HT82K68A-20 데이터 시트보기 (PDF) - Holtek Semiconductor

부품명

상세내역

제조사

HT82K68A-20 Datasheet PDF : 39 Pages

| |||

HT82K68A

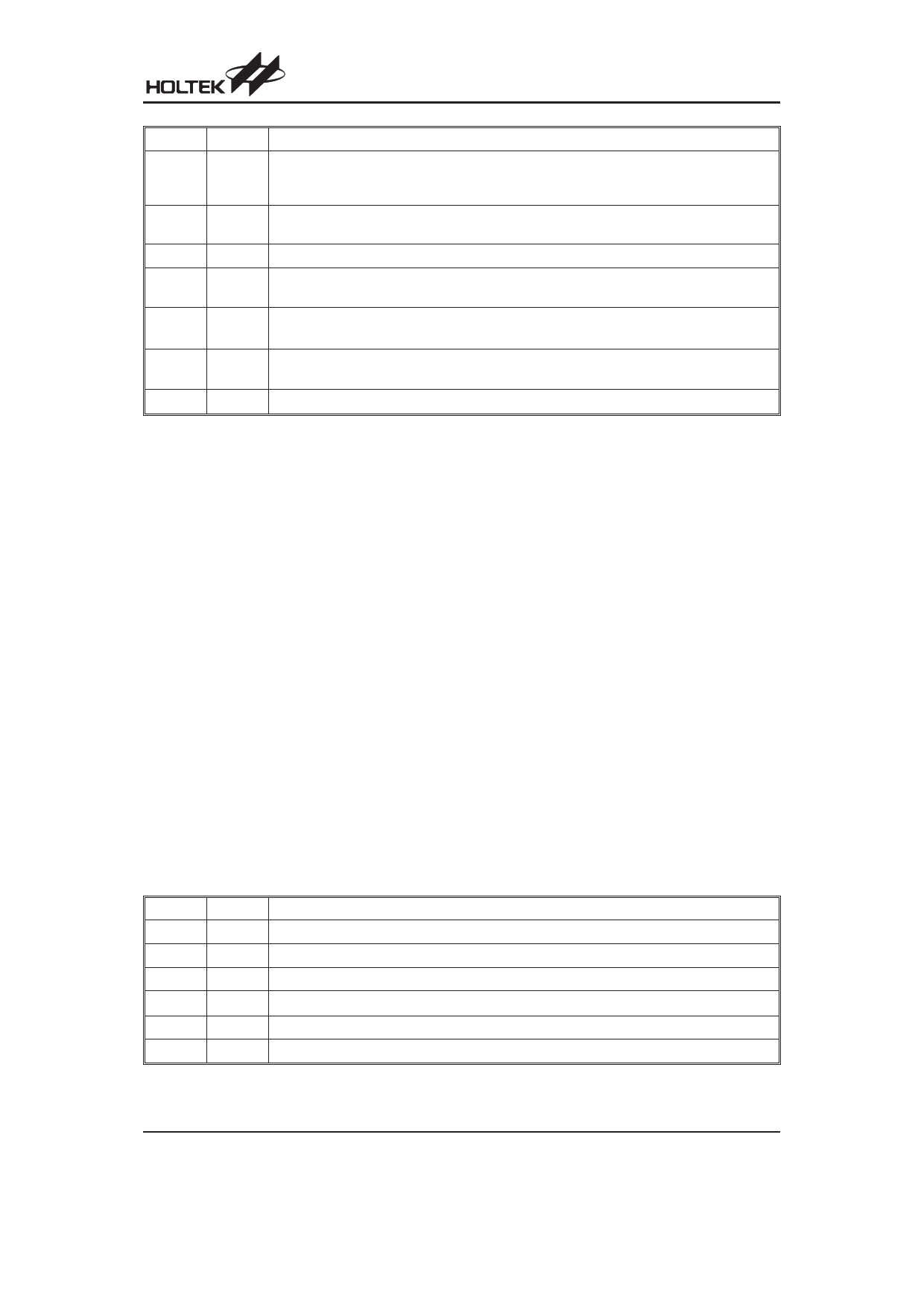

Bit No.

0

1

2

3

4

5

6, 7

Label

C

AC

Z

OV

PDF

TO

¾

Function

C is set if an operation results in a carry during an addition operation or if a borrow does not

take place during a subtraction operation; otherwise C is cleared. C is also affected by a rotate

through carry instruction.

AC is set if an operation results in a carry out of the low nibbles in addition or if no borrow from

the high nibble into the low nibble in subtraction; otherwise AC is cleared.

Z is set if the result of an arithmetic or logical operation is zero; otherwise Z is cleared.

OV is set if an operation results in a carry into the highest-order bit but not a carry out of the

highest-order bit, or vice versa; otherwise OV is cleared.

PDF is cleared when either a system power-up or executing the ²CLR WDT² instruction.

PDF is set by executing a ²HALT² instruction.

TO is cleared by a system power-up or executing the ²CLR WDT² or ²HALT² instruction.

TO is set by a WDT time-out.

Unused bit, read as ²0²

Status (0AH) Register

Interrupt

The HT82K68A provides an internal timer counter inter-

rupt and an external interrupt shared with PC2. The in-

terrupt control register (INTC;0BH) contains the

interrupt control bits to set not only the enable/disable

status but also the interrupt request flags.

Once an interrupt subroutine is serviced, all other inter-

rupts will be blocked (by clearing the EMI bit). This

scheme may prevent any further interrupt nesting. Other

interrupt requests may occur during this interval but only

the interrupt request flag is recorded. If a certain inter-

rupt requires servicing within the service routine, the

EMI bit and the corresponding bit of the INTC may be

set to allow interrupt nesting. If the stack is full, the inter-

rupt request will not be acknowledged, even if the re-

lated interrupt is enabled, until the SP is decremented. If

immediate service is desired, the stack must be pre-

vented from becoming full.

All these kinds of interrupt have the wake-up capability.

As an interrupt is serviced, a control transfer occurs by

pushing the program counter onto the stack followed by

a branch to a subroutine at the specified location in the

program memory. Only the program counter is pushed

onto the stack. If the contents of the register and Status

register (STATUS) are altered by the interrupt service

program which corrupt the desired control sequence,

the contents should be saved in advance.

The internal timer counter interrupt is initialized by set-

ting the timer counter interrupt request flag (T0F; bit 5 of

INTC), which is normally caused by a timer counter

overflow. When the interrupt is enabled, and the stack is

not full and the T0F bit is set, a subroutine call to location

08H will occur. The related interrupt request flag (T0F)

will be reset and the EMI bit cleared to disable further in-

terrupts.

The external interrupt is shared with PC2. The external

interrupt is activated, the related interrupt request flag

(EIF; bit4 of INTC) is then set. When the interrupt is en-

abled, the stack is not full, and the external interrupt is

active, a subroutine call to location 04H will occur. The

interrupt request flag (EIF) and EMI bits will also be

cleared to disable other interrupts.

The external interrupt (PC2) can be triggered by a high

to low transition, or a low to high transition of the PC2,

which is dependent on the output level of the PE0. When

PE0 is output high, the external interrupt is triggered by

Bit No.

0

1

2

3, 6~7

4

5

Label

EMI

EEI

ET0I

¾

EIF

T0F

Function

Controls the master (global) interrupt (1= enabled; 0= disabled)

Control the external interrupt

Controls the timer counter interrupt (1= enabled; 0= disabled)

Unused bit, read as ²0²

External interrupt flag

Internal timer counter request flag (1= active; 0= inactive)

INTC (0BH) Register

Rev. 1.70

9

December 26, 2005