CMX605 데이터 시트보기 (PDF) - MX-COM Inc

부품명

상세내역

제조사

CMX605 Datasheet PDF : 26 Pages

| |||

Digital Line to POTS Interface

Page 10 of 26

CMX605 Preliminary Information

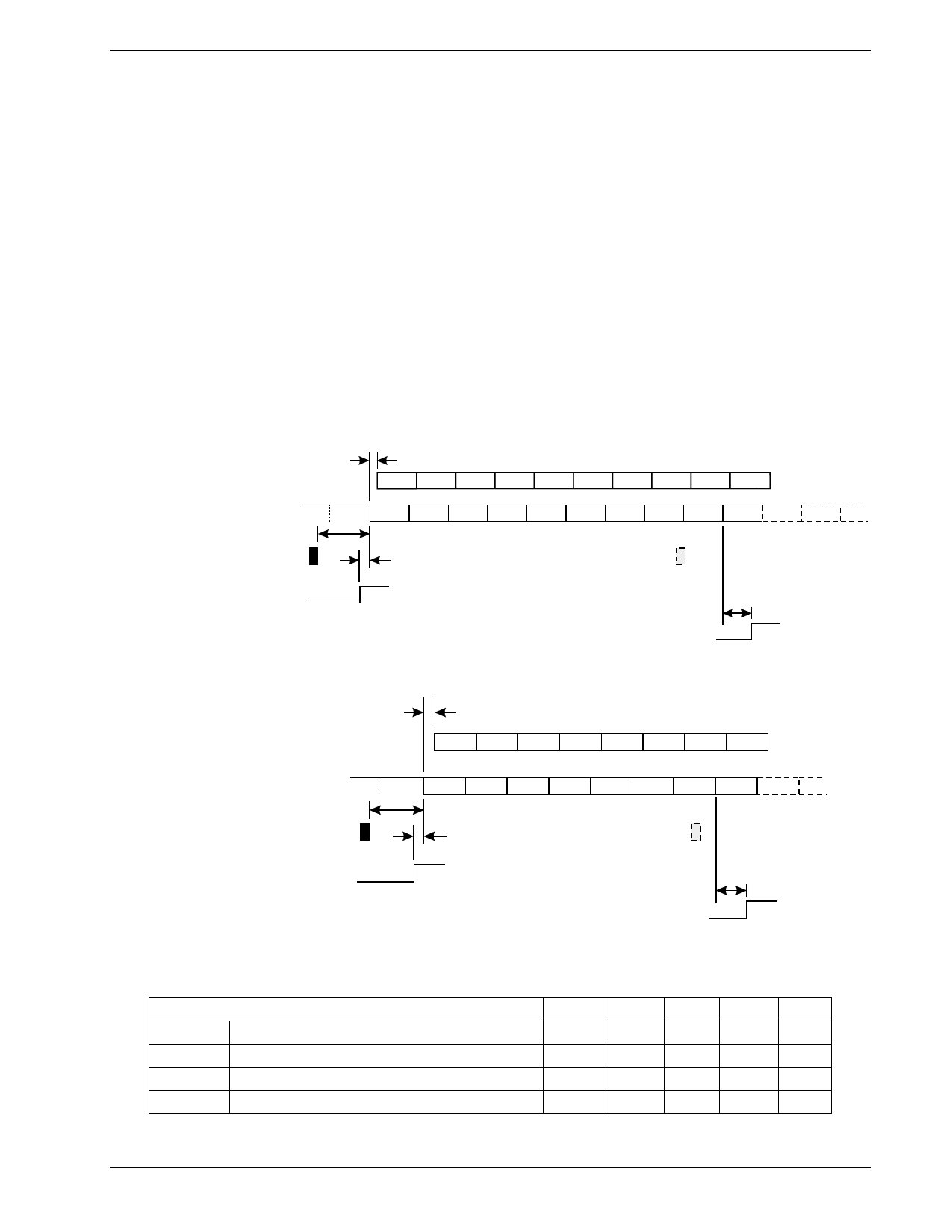

4.6 Tx UART

This block connects the µC, via the ‘C-BUS’ interface, to the FSK Encoder.

The block can be programmed to convert transmit data from 8-bit bytes to asynchronous data characters by

adding Start and Stop bits. The transmit data is then passed to the FSK Encoder.

Data to be transmitted should be loaded by the µC into the TX DATA Register when the Tx Data Ready bit (bit

6) of the STATUS Register goes high. The data will then be treated by the Tx UART block in one of two ways,

depending on the setting of bit 1 of the SETUP Register:

If bit 1 of the SETUP Register is ‘0’ (Tx Sync mode) then the 8 bits from the TX DATA Register will be

transmitted sequentially at 1200bps, LSB (D0) first.

If bit 1 of the SETUP Register is ‘1’ (Tx Async mode) then bits will be transmitted as asynchronous data

characters at 1200bps according to the following format:

One Start bit (Space)

Eight Data bits (D0-D7) from the TX DATA Register, with the LSB (D0) transmitted first

One Stop bit (Mark)

Failure to load the TX DATA Register with a new value when required will result in bit 7 (Tx Data Underflow) of

the STATUS Register being set to ‘1’. If the ‘Tx Async’ mode of operation is selected then a continuous Mark

(‘1’) signal will be transmitted until a new value is loaded into TX DATA. If the ‘Tx Sync’ mode is selected then

the byte already in the TX DATA Register will be re-transmitted.

Analog FSK signal:

tFSK

Start D0 D1 D2 D3 D4 D5 D6 D7 Stop

Digital Tx signal:

tDLY

TX DATA Register loaded:

Start D0 D1 D2 D3 D4 D5 D6 D7 Stop Start D0

tDRDY

Tx Data Ready flag bit:

tUFL

Tx Data Underflow flag bit:

Figure 3: Transmit UART Function (Async)

Analog FSK signal:

tFSK

D0 D1 D2 D3 D4 D5 D6 D7

Digital Tx signal:

tDLY

TX DATA Register loaded:

D0 D1 D2 D3 D4 D5 D6 D7 D0

tDRDY

Tx Data Ready flag bit:

tUFL

Tx Data Underflow flag bit:

Figure 4: Transmit UART Function (Sync)

4.6.1 Tx UART Timings

Typical UART Timings (See Figure 3 and Figure 4) Notes Min. Typ. Max. Unit

tFSK

tDLY

tDRDY

tUFL

(delay through the modulator)

(1 bit-period)

(1/4 bit-period)

(3/4 bit-period)

106

µs

833

µs

208

µs

625

µs

¤2001 MX-COM, Inc.

www.mxcom.com tel: 800 638 5577 336 744 5050 fax: 336 744 5054

Doc. # 20480195.005

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.