MA82380 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

MA82380 Datasheet PDF : 134 Pages

| |||

M82380

1 1 1 DMA CONTROLLER

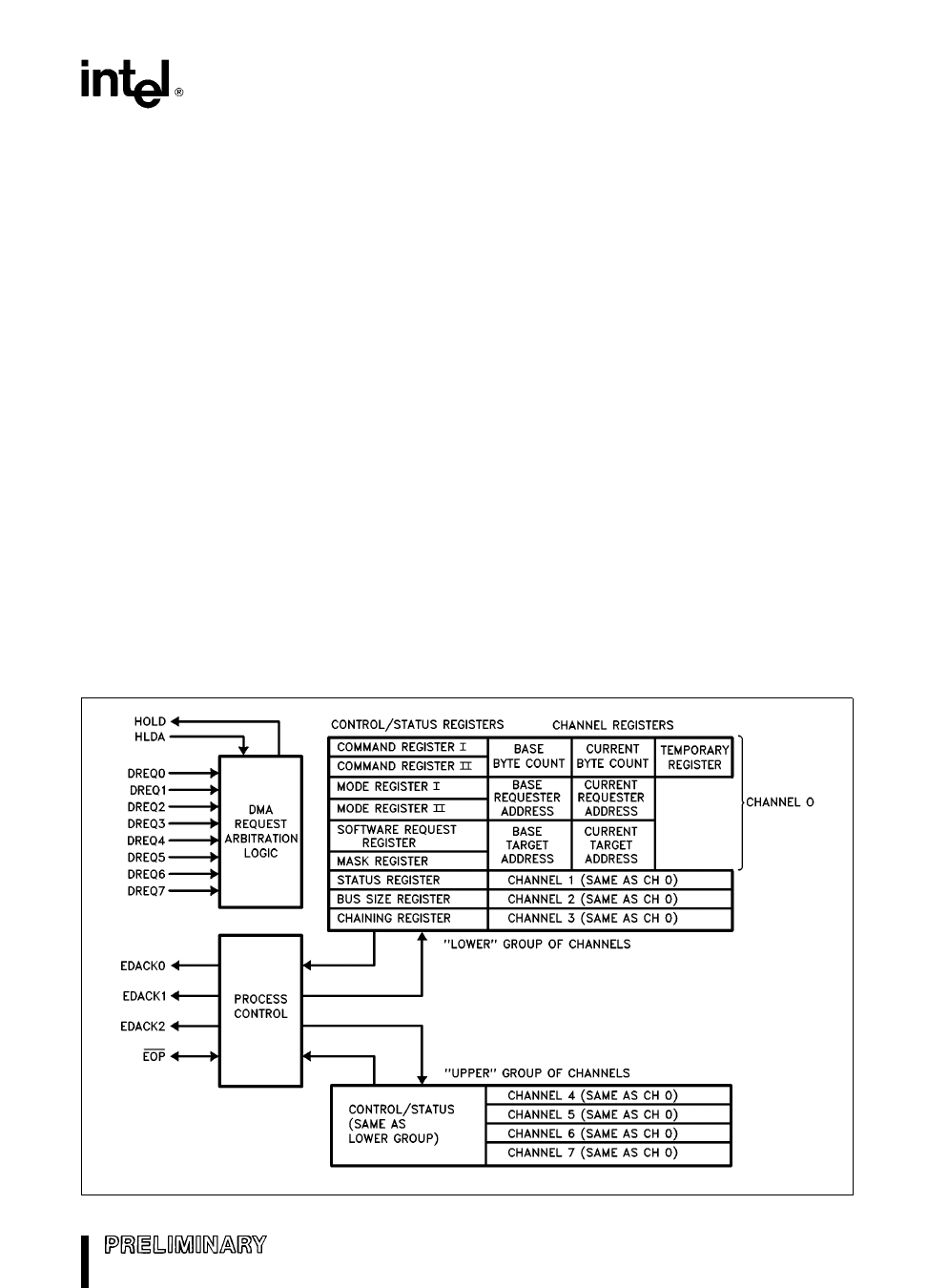

The M82380 contains a high-performance 8-chan-

nel 32-bit DMA controller It is capable of transfer-

ring any combination of bytes words and double

words The addresses of both source and destina-

tion can be independently incremented decrement-

ed or held constant and cover the entire 32-bit

physical address space of the i386 microprocessor

It can disassemble and assemble misaligned data

via a 32-bit internal temporary data storage register

Data transferred between devices of different data

path widths can also be assembled and disassem-

bled using the internal temporary data storage regis-

ter The DMA Controller can also transfer aligned

data between I O and memory on the fly allowing

data transfer rates up to 32 megabytes per second

for an M82380 operating at 16 MHz Figure 2 illus-

trates the functional components of the DMA Con-

troller

There are twenty-four general status and command

registers in the M82380 DMA Controller Through

these registers any of the channels may be pro-

grammed into any of the possible modes The oper-

ating modes of any one channel are independent of

the operation of the other channels

Each channel has three programmable registers

which determine the location and amount of data to

be transferred

Byte Count Register Number of bytes to trans-

fer (24-bits)

Requester Register Address of memory or pe-

ripheral which is requesting DMA service (32-

bits)

Target Register Address of peripheral or mem-

ory which will be accessed (32-bits)

There are also port addresses which when ac-

cessed cause the M82380 to perform specific func-

tions The actual data written does not matter the

act of writing to the specific address causes the

command to be executed The commands which op-

erate in this mode are Master Clear Clear Terminal

Count Interrupt Request Clear Mask Register and

Clear Byte Pointer Flip-Flop

DMA transfers can be done between all combina-

tions of memory and I O memory-to-memory mem-

ory-to-I O I O-to-memory and I O-to-I O DMA

service can be requested through software and or

hardware Hardware DMA acknowledge signals are

available for all channels (except channel 4) through

an encoded 3-bit DMA acknowledge bus

(EDACK0 – 2)

Figure 2 M82380 DMA Controller

271070 – 3

7