AS5SS256K36 데이터 시트보기 (PDF) - Micross Components

부품명

상세내역

제조사

AS5SS256K36 Datasheet PDF : 17 Pages

| |||

SSRAM

AS5SS256K36

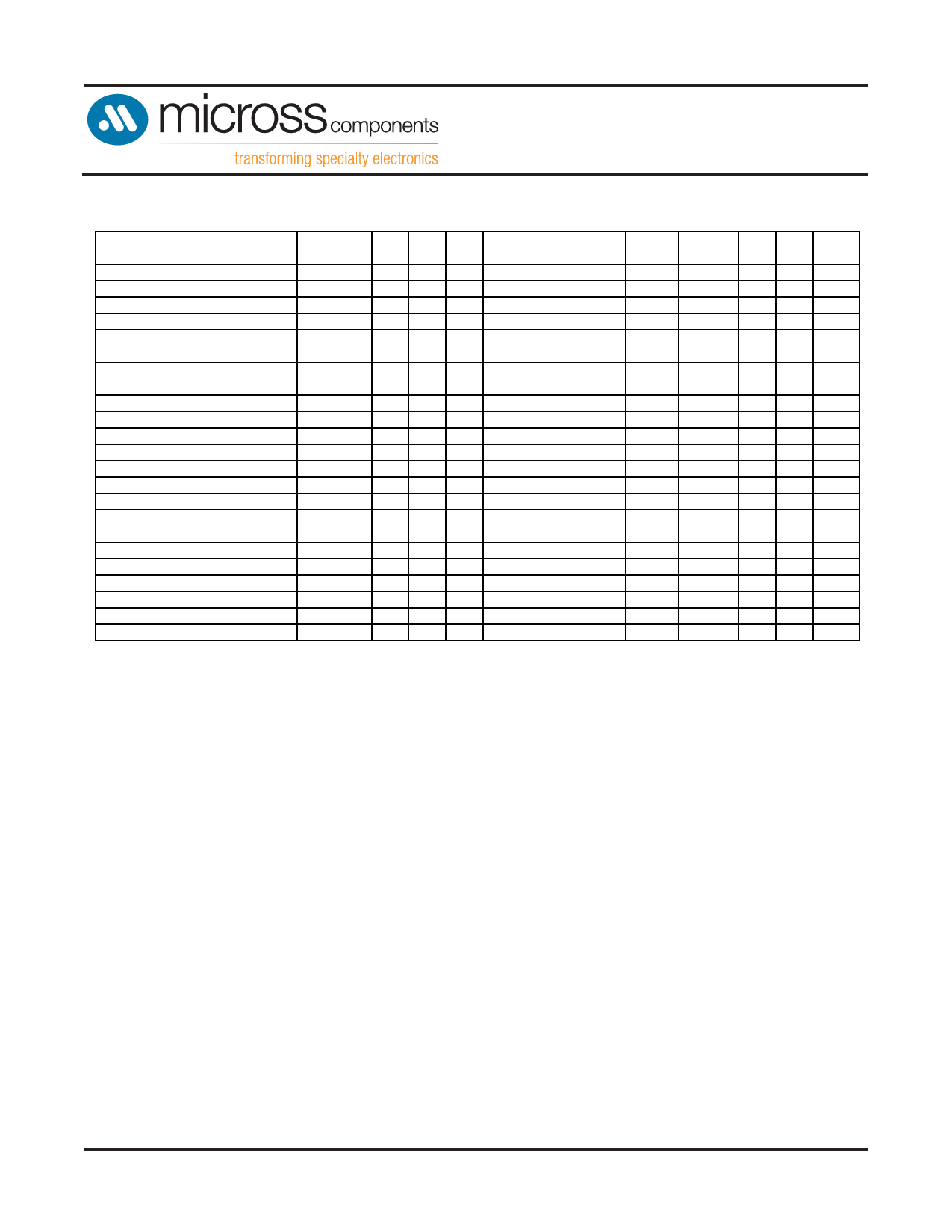

TRUTH TABLE

OPERATION

Deselected Cycle, Power-Down

Deselected Cycle, Power-Down

Deselected Cycle, Power-Down

Deselected Cycle, Power-Down

Deselected Cycle, Power-Down

SNOOZE MODE, Power-Down

READ Cycle, Begin Burst

READ Cycle, Begin Burst

WRITE Cycle, Begin Burst

READ Cycle, Begin Burst

READ Cycle, Begin Burst

READ Cycle, Continue Burst

READ Cycle, Continue Burst

READ Cycle, Continue Burst

READ Cycle, Continue Burst

WRITE Cycle, Continue Burst

WRITE Cycle, Continue Burst

READ Cycle, Suspend Burst

READ Cycle, Suspend Burst

READ Cycle, Suspend Burst

READ Cycle, Suspend Burst

WRITE Cycle, Suspend Burst

WRITE Cycle, Suspend Burst

ADDRESS

USED

CE\

CE2\ CE2

ZZ

ADSP\ ADSC\

ADV\

None

HXX L

X

L

X

None

LXLL

L

X

X

None

L HX L

L

X

X

None

LXLL

H

L

X

None

L HX L

H

L

X

None

XXXH

X

X

X

External L L H L

L

X

X

External L L H L

L

X

X

External L L H L

H

L

X

External L L H L

H

L

X

External L L H L

H

L

X

Next

XXXL

H

H

L

Next

XXXL

H

H

L

Next

HXX L

X

H

L

Next

HXX L

X

H

L

Next

XXXL

H

H

L

Next

HXX L

X

H

L

Current X X X L

H

H

H

Current X X X L

H

H

H

Current H X X L

X

H

H

Current H X X L

X

H

H

Current X X X L

H

H

H

Current H X X L

X

H

H

WRITE\ OE\ CLK DQ

X

X L-H High-Z

X

X L-H High-Z

X

X L-H High-Z

X

X L-H High-Z

X

X L-H High-Z

X

X X High-Z

X

L L-H Q

X

H L-H High-Z

L

X L-H D

H

L L-H Q

H

H L-H High-Z

H

L L-H Q

H

H L-H High-Z

H

L L-H Q

H

H L-H High-Z

L

X L-H D

L

X L-H D

H

L L-H Q

H

H L-H High-Z

H

L L-H Q

H

H L-H High-Z

L

X L-H D

L

X L-H D

NOTE:

1. X means “Don’t Care.” \ means active LOW. H Means logic HIGH. L means logic LOW.

2. For WRITE\, L means any one or more byte write enable signals (BWa\, BWb\, BWc\, or BWd\) and BWE\ are LOW or

GW\ is LOW. WRITE\ = H for all BWx\, BWE\, GW\ HIGH.

3. BWa\ enables WRITEs to DQa pins, DQPa. BWb\ enables WRITEs to DQb pins, DQPb. BWc\ enables WRITEs to DQc

pins, DQPc. BWd\ enables WRITEs to DQd pins, DQPd.

4. All inputs except OE\ and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

5. Wait states are inserted by suspending burst.

6. For a WRITE operation following a READ operation, OE\ must be HIGH before the input data setup time and held HIGH

throughout the input data hold time.

7. This device contains circuitry that will ensure the outputs will be High-Z during power-up.

8. ADSP\ LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more

byte write enable signals and BWE\ LOW or GW\ LOW for the subsequent L-H edge of CLK. Refer to WRITE timing

diagram for clarification.

AS5SS256K36

Rev. 4.4 10/13

Micross Components reserves the right to change products or specifications without notice.

6