APU429 데이터 시트보기 (PDF) - APLUS INTEGRATED CIRCUITS

부품명

상세내역

제조사

APU429 Datasheet PDF : 18 Pages

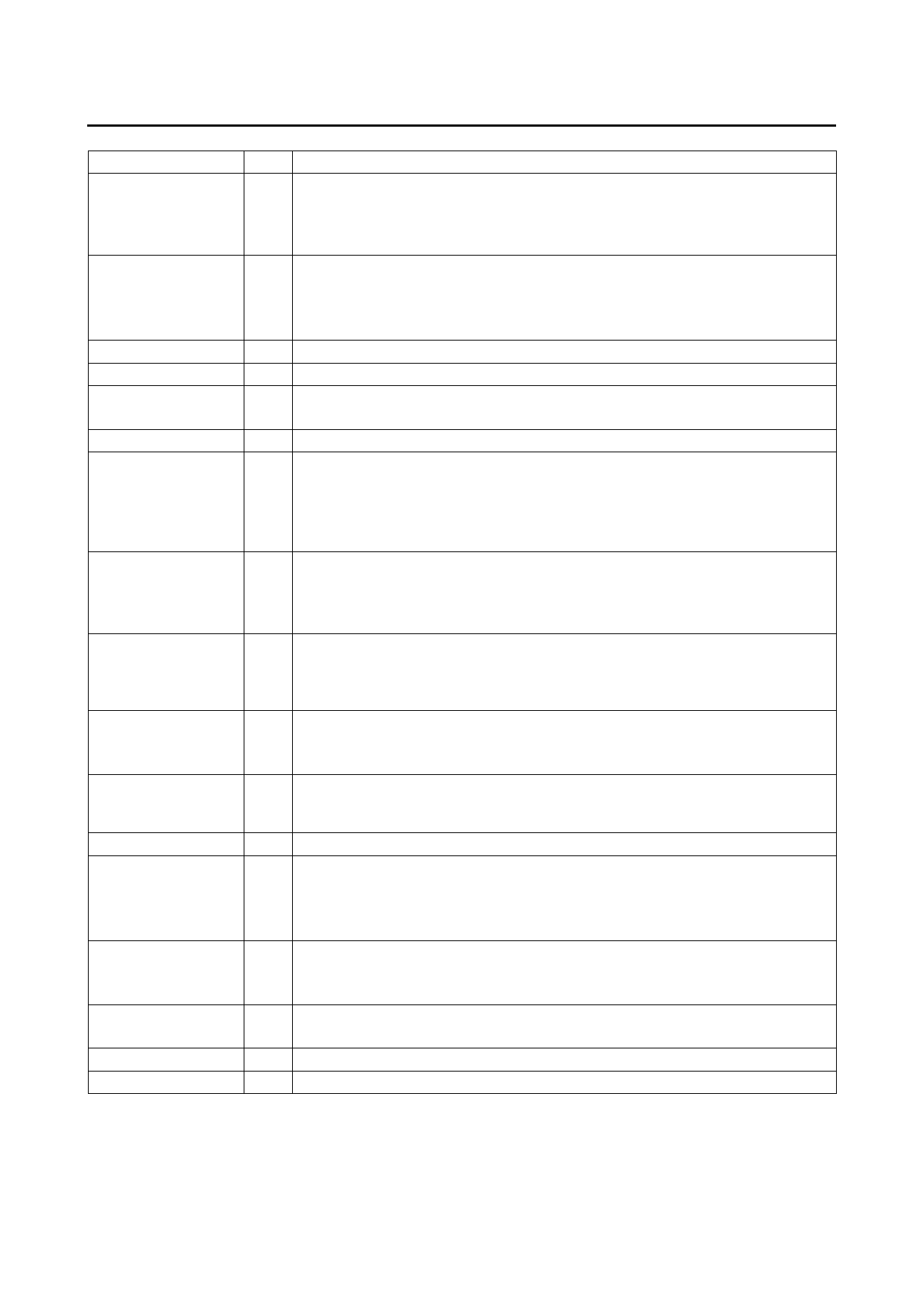

| |||

Pad Name

XTIN

XTOUT

CFIN

CFOUT

COM1~8

SEG1~10

SEG11~26/KO1~16

SEG27~42

IOA1~4

IOB1~4

IOC1~4

IOD1~4

S1~4

KI1~4

RFC

EL

CC

RR

RT

RH

ELC

ELP

ALM BZB

BZ

PWM1, 2

GND

I/O

Description

Time based counter frequency (Clock specified. LCD alternating frequency.

I Alarm signal frequency.) or system clock oscillation.

O 32KHz crystal oscillator.

Oscillation stops at the execution of STOP instruction.

System clock oscillation.

I Connected with ceramic resonator.

O Connected with RC oscillation circuit.

Oscillation stops at the execution of STOP or SLOW instruction.

O Output pins for supplying voltage to drive the common pins of the LCD panel.

O Output pins for LCD panel segment.

Output pins for LCD panel segment.

O Key strobe function, share pins as key scan output.

O Output pins for LCD panel segment.

Input/Output port A, can use software to define the internal pull-low resistor

and chattering clock in order to reduce input bounce and generate an

I/O interrupt.

This port shares pins with SEG35~38 and is set by mask option.

This port also shares pins with CC, RR, RT and RH, and is set by mask option.

Input/Output port B.

I/O IOB port shares pins with SEG31~34, and is set by mask option.

This port also shares pins with ELC, ELP, BZB and BZ, and is set by mask

option.

Input/Output port C, can use software to define internal pull-low/low-level hold

I/O resistor and chattering clock in order to reduce input bounce and generate an

interrupt or keyboard scanning function with ELC, ELP, BZB and BZ, and is

set by mask option.

Input/Output port D.

I/O This port shares pins with SEG27~30 and is set by mask option.

IOD3, 4 shares pins with PWM1, 2 and is set by mask option.

Input ports by mask option to internal pull-low/low-level hold resistor and

I chattering clock in order to reduce input bounce and generate an interrupt or

HALT or STOP release.

I Key scan input, this port shares pins with IOC1~4 and is set by mask option.

I 1 input pin and 3 output pins for RFC application.

O This port shares pins with SEG35~38 and is set by mask option.

O This port shares pins with IOA1~4 and is set by mask option.

O

O Output port for EL-light.

O This port shares pins with SEG31, 32 and is set by mask option.

This port shares pins with IOB1, 2 and is set by mask option.

O Output port for alarm, frequency or melody generator.

This port shares pins with IOB3, 4 and is set by mask option.

O 6/8-Bit PWM output; set by mask option.

Negative supply voltage.

Preliminary

4

Ver. 0.0