EN6360QI 데이터 시트보기 (PDF) - Altera Corporation

부품명

상세내역

제조사

EN6360QI

EN6360QI Datasheet PDF : 24 Pages

| |||

EN6360QI

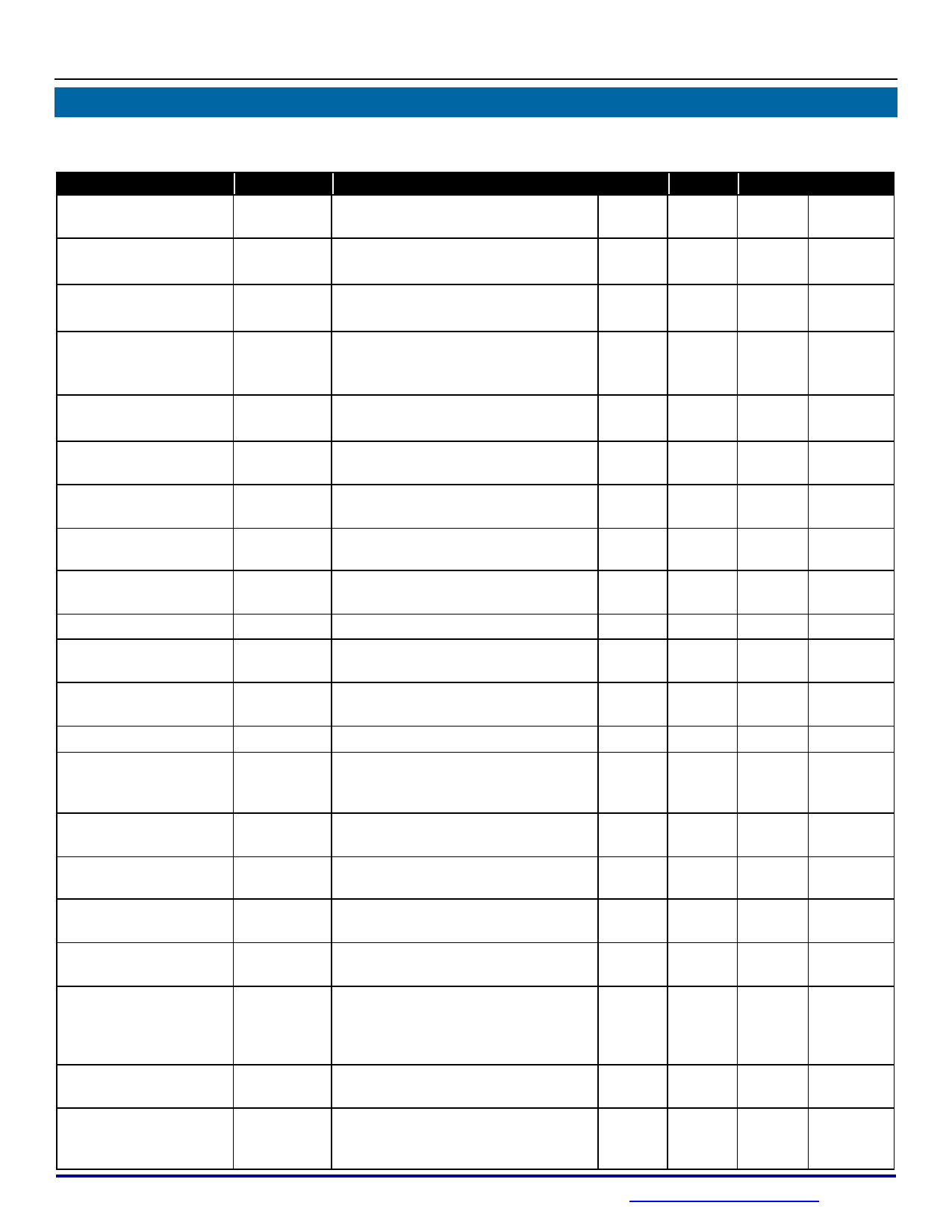

Electrical Characteristics

NOTE: VIN=6.6V, Minimum and Maximum values are over operating ambient temperature range unless otherwise noted.

Typical values are at TA = 25°C.

PARAMETER

Operating Input

Voltage

SYMBOL

VIN

TEST CONDITIONS

MIN TYP MAX UNITS

2.5

6.6

V

VFB Pin Voltage

VVFB

VFB Pin Voltage (Load

and Temperature)

VVFB

Internal Voltage Reference at:

VIN = 5V, ILOAD = 0, TA = 25°C

0.594 0.600 0.606

V

0A ≤ ILOAD ≤ 8A

Starting Date Code: X501 or greater

0.591

0.600

.609

V

VFB Pin Voltage

(Line, Load and

VVFB

Temperature)

2.5V ≤ VIN ≤ 6.6V

0A ≤ ILOAD ≤ 8A

0.588 0.600 0.612

V

VFB Pin Input Leakage

Current

IVFB

VFB Pin Input Leakage Current

(Note 4)

-10

10

nA

Shut-Down Supply

Current

IS

Power Supply Current with

ENABLE=0

1.5

mA

Under Voltage Lock-

out – VIN Rising

VUVLOR

Voltage Above Which UVLO is Not

Asserted

2.2

V

Under Voltage Lock-

out – VIN Falling

VUVLOF

Voltage Below Which UVLO is

Asserted

2.1

V

Drop Out Voltage

VDO

VINMIN – VOUT at Full Load

400

800

Drop Out Resistance

Continuous Output

Current

RDO

IOUT_SRC

Input to Output Resistance

50

100

0

8

Over Current Trip

Level

IOCP

Sourcing Current

16

Switching Frequency

External SYNC Clock

Frequency Lock

Range

FSW

FPLL_LOCK

RFADJ = 4.42 kΩ, VIN = 5V

SYNC Clock Input Frequency

Range

0.9

1.2

1.5

0.9*Fsw Fsw 1.1*Fsw

S_IN Clock Amplitude

– Low

VS_IN_LO

SYNC Clock Logic Low

0

0.8

S_IN Clock Amplitude

– High

VS_IN_HI

SYNC Clock Logic High

1.8

2.5

S_IN Clock Duty Cycle

(PLL)

DCS_INPLL

M/S Pin Float or Low

20

80

S_IN Clock Duty Cycle

(PWM)

DCS_INPWM

M/S Pin High

10

90

Allowable Pre-bias as a Fraction of

Pre-Bias Level

VPB

Programmed Output Voltage for

Monotonic start up. Minimum Pre-

20

75

bias Voltage = 300mV.

Non-Monotonicity

VPB_NM

Allowable Non-monotonicity Under

Pre-bias Startup

100

VOUT Range for POK =

High

Range of Output Voltage as a

Fraction of Programmed Value

90

120

When POK is Asserted. (Note 3)

mV

mΩ

A

A

MHz

MHz

V

V

%

%

%

mV

%

06489

March 24, 2015

www.altera.com/enpirion, Page 5

Rev G