M95320-DRE 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

M95320-DRE Datasheet PDF : 42 Pages

| |||

Operating features

3

Operating features

M95320-DRE

3.1

Active power and Standby power modes

When Chip Select (S) is low, the device is selected and in the Active power mode.

When Chip Select (S) is high, the device is deselected. If a Write cycle is not currently in

progress, the device then goes in to the Standby power mode, and the device consumption

drops to ICC1, as specified in Table 12.

3.2

SPI modes

The device can be driven by a microcontroller with its SPI peripheral running in either of the

two following modes:

• CPOL=0, CPHA=0

• CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and

output data is available from the falling edge of Serial Clock (C).

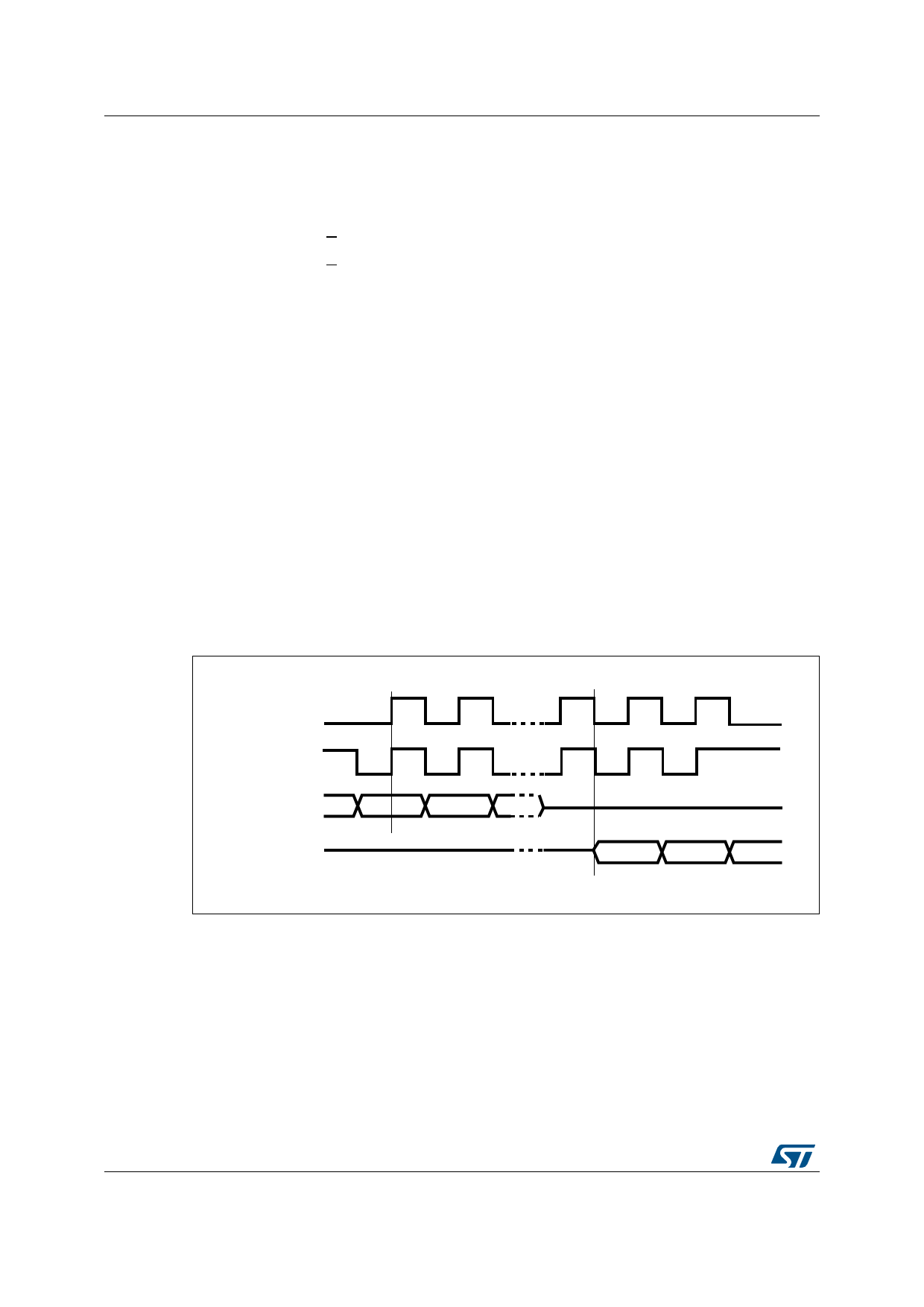

The difference between the two modes, as shown in Figure 3, is the clock polarity when the

bus master is in Stand-by mode and not transferring data:

• C remains at 0 for (CPOL=0, CPHA=0)

• C remains at 1 for (CPOL=1, CPHA=1)

Figure 3. SPI modes supported

#0/, #0(!

#

#

$

-3"

1

-3"

!)"

10/42

DocID027471 Rev 2