ADSP-BF539 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADSP-BF539 Datasheet PDF : 68 Pages

| |||

ADSP-BF539/ADSP-BF539F

The ADSP-BF539/ADSP-BF539F processor DMA controllers

support both 1-dimensional (1D) and 2-dimensional (2D)

DMA transfers. DMA transfer initialization can be imple-

mented from registers or from sets of parameters called

descriptor blocks.

The 2D DMA capability supports arbitrary row and column

sizes up to 64K elements by 64K elements, and arbitrary row

and column step sizes up to ±32K elements. Furthermore, the

column step size can be less than the row step size, allowing

implementation of interleaved data streams. This feature is

especially useful in video applications where data can be de-

interleaved on the fly.

Examples of DMA types supported by the ADSP-BF539/ADSP-

BF539F processor DMA controller include:

• A single, linear buffer that stops upon completion

• A circular, auto-refreshing buffer that interrupts on each

full or fractionally full buffer

• 1-D or 2-D DMA using a linked list of descriptors

• 2-D DMA using an array of descriptors, specifying only the

base DMA address within a common page

In addition to the dedicated peripheral DMA channels, there are

four memory DMA channels provided for transfers between the

various memories of the ADSP-BF539/ADSP-BF539F processor

system. This enables transfers of blocks of data between any of

the memories—including external SDRAM, ROM, SRAM, and

flash memory—with minimal processor intervention. Memory

DMA transfers can be controlled by a very flexible descriptor

based methodology or by a standard register based autobuffer

mechanism.

REAL TIME CLOCK

The ADSP-BF539/ADSP-BF539F processor Real Time Clock

(RTC) provides a robust set of digital watch features, including

current time, stopwatch, and alarm. The RTC is clocked by a

32.768 KHz crystal external to the ADSP-BF539/ADSP-BF539F

processor. The RTC peripheral has dedicated power supply pins

so that it can remain powered up and clocked even when the

rest of the processor is in a low power state. The RTC provides

several programmable interrupt options, including interrupt

per second, minute, hour, or day clock ticks, interrupt on pro-

grammable stopwatch countdown, or interrupt at a

programmed alarm time.

The 32.768 KHz input clock frequency is divided down to a

1 Hz signal by a prescaler. The counter function of the timer

consists of four counters: a 60 second counter, a 60 minute

counter, a 24 hour counter, and an 32,768 day counter.

When enabled, the alarm function generates an interrupt when

the output of the timer matches the programmed value in the

alarm control register. There are two alarms: The first alarm is

for a time of day. The second alarm is for a day and time of that

day.

The stopwatch function counts down from a programmed

value, with one second resolution. When the stopwatch is

enabled and the counter underflows, an interrupt is generated.

Preliminary Technical Data

Like the other peripherals, the RTC can wake up the ADSP-

BF539/ADSP-BF539F processor from Sleep mode upon genera-

tion of any RTC wakeup event. Additionally, an RTC wakeup

event can wake up the ADSP-BF539/ADSP-BF539F processor

from Deep Sleep mode, and wake up the on-chip internal volt-

age regulator from a powered down state.

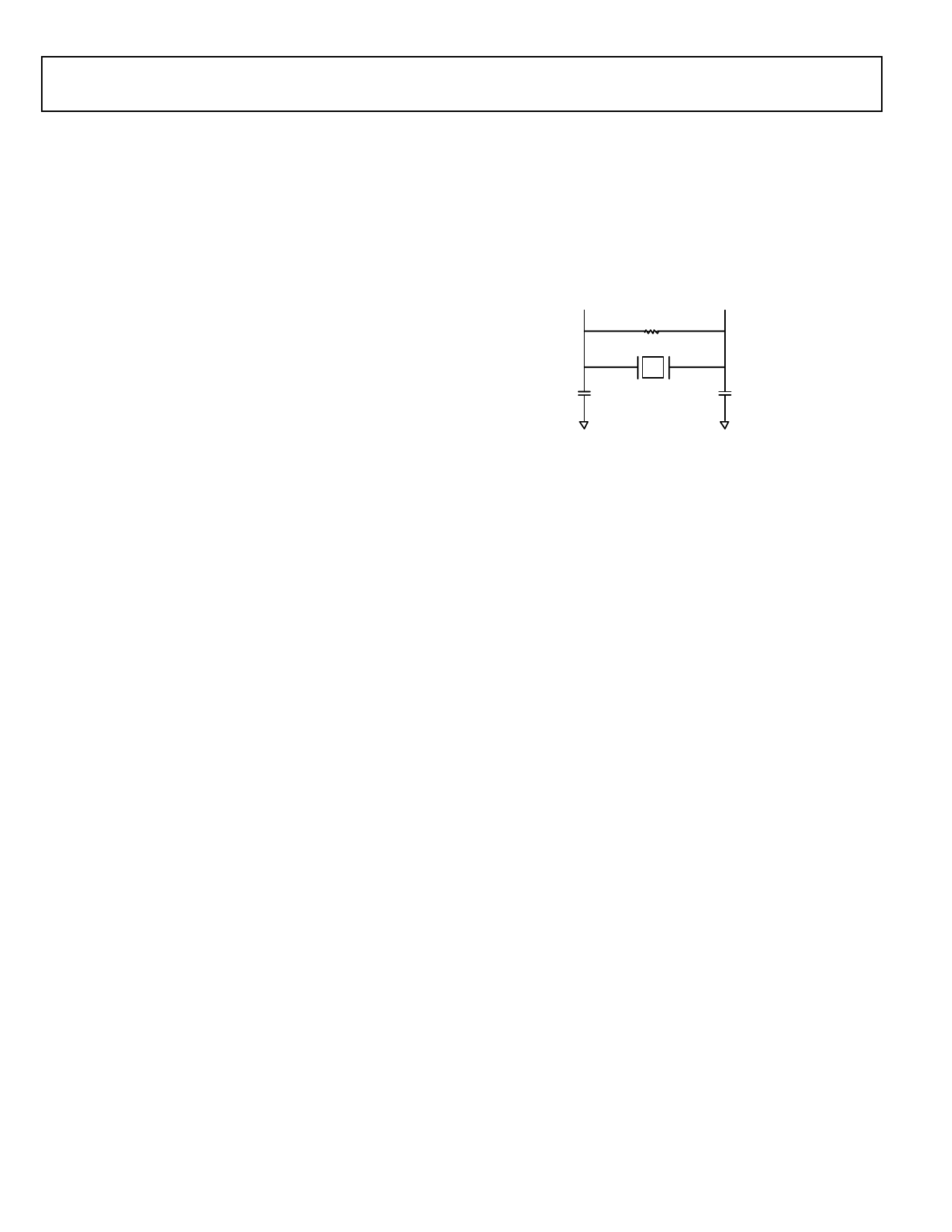

Connect RTC pins RTXI and RTXO with external components

as shown in Figure 5.

RTXI

RTXO

R1

X1

C1

C2

SUGGESTED COMPONENTS:

ECLIPTEK EC38J (THROUGH-HOLE PACKAGE)

EPSON MC405 12 pF LOAD (SURFACE-MO UNT PACKAGE)

C1 = 22 pF

C2 = 22 pF

R1 = 10 MΩ

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECI FIED FOR X1.

CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2

SPECIFI CATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

Figure 5. External Components for RTC

WATCHDOG TIMER

The ADSP-BF539/ADSP-BF539F processor includes a 32-bit

timer that can be used to implement a software watchdog func-

tion. A software watchdog can improve system availability by

forcing the processor to a known state through generation of a

hardware reset, non-maskable interrupt (NMI), or general pur-

pose interrupt, if the timer expires before being reset by

software. The programmer initializes the count value of the

timer, enables the appropriate interrupt, then enables the timer.

Thereafter, the software must reload the counter before it

counts to zero from the programmed value. This protects the

system from remaining in an unknown state where software,

which would normally reset the timer, has stopped running due

to an external noise condition or software error.

If configured to generate a hardware reset, the watchdog timer

resets both the core and the ADSP-BF539/ADSP-BF539F pro-

cessor peripherals. After a reset, software can determine if the

watchdog was the source of the hardware reset by interrogating

a status bit in the watchdog timer control register.

The timer is clocked by the system clock (SCLK), at a maximum

frequency of fSCLK.

TIMERS

There are four general purpose programmable timer units in the

ADSP-BF539/ADSP-BF539F processor. Three timers have an

external pin that can be configured either as a Pulse Width

Modulator (PWM) or timer output, as an input to clock the

timer, or as a mechanism for measuring pulse widths and peri-

Rev. PrF | Page 10 of 68 | September 2006