ADCMP604BKSZ-R2 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADCMP604BKSZ-R2

ADCMP604BKSZ-R2 Datasheet PDF : 14 Pages

| |||

Data Sheet

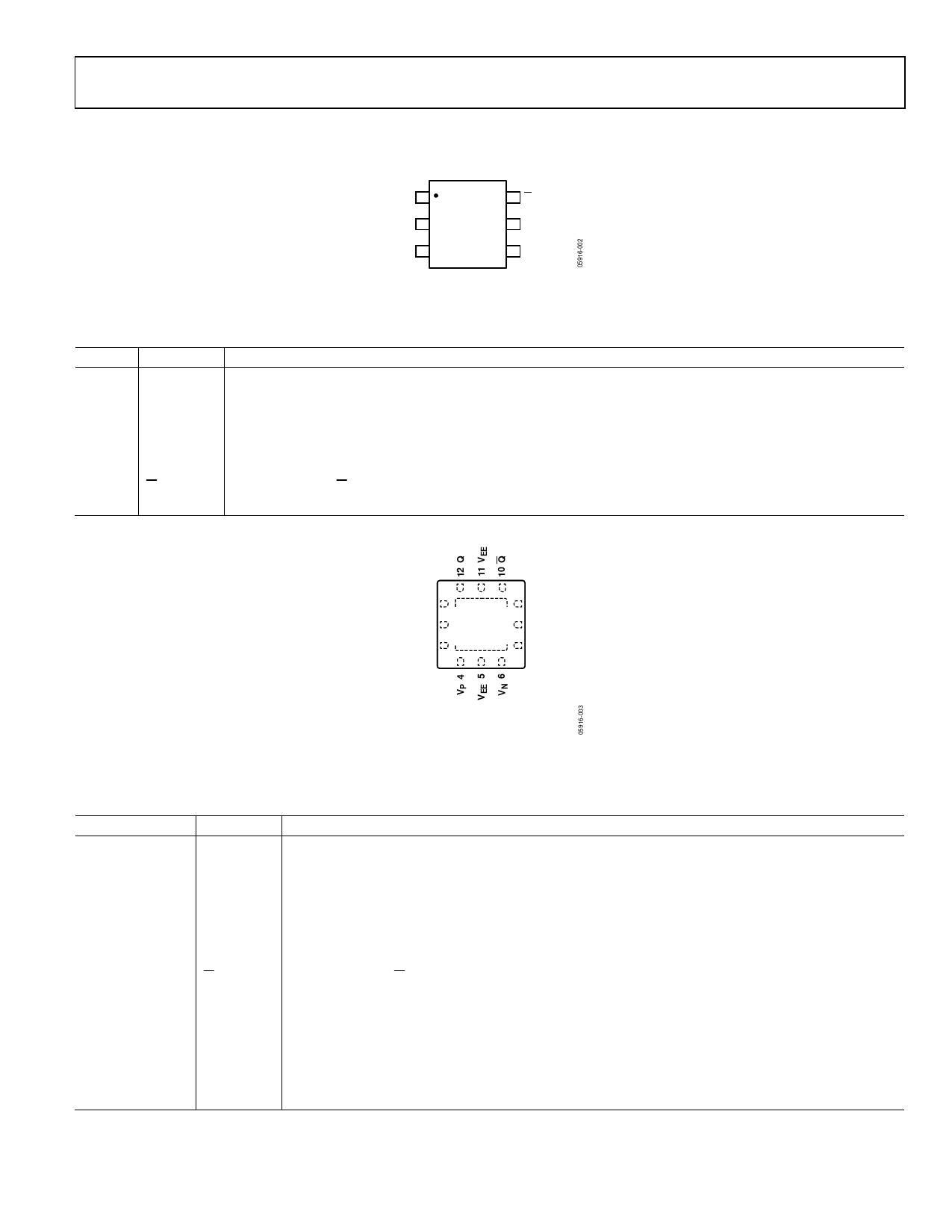

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

ADCMP604/ADCMP605

Q1

6Q

ADCMP604

VEE 2 TOP VIEW 5 VCCI/VCCO

(Not to Scale)

VP 3

4 VN

Figure 3. ADCMP604 Pin Configuration

Table 5. ADCMP604 Pin Function Descriptions (6-Lead SC70)

Pin No. Mnemonic Description

1

Q

Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, VP, is greater than the

analog voltage at the inverting input, VN.

2

VEE

Negative Supply Voltage.

3

VP

Noninverting Analog Input.

4

VN

Inverting Analog Input.

5

VCCI/VCCO

Input Section Supply/Output Section Supply. VCCI and VCCO are shared pin.

6

Q

Inverting Output. Q is at logic low if the analog voltage at the noninverting input, VP, is greater than the analog

voltage at the inverting input, VN.

VCCO 1

VCCI 2

VEE 3

ADCMP605

TOP VIEW

(Not to Scale)

9 VEE

8 LE/HYS

7 SDN

NOTES

1. EXPOSED PAD. IF CONNECTED, THE

EPAD MUST BE CONNECTED TO VEE.

Figure 4. ADCMP605 Pin Configuration

Table 6. ADCMP605 Pin Function Descriptions (12-Lead LFCSP_WQ)

Pin No.

Mnemonic Description

1

VCCO

Output Section Supply.

2

VCCI

Input Section Supply.

3, 5, 9, 11

VEE

Negative Supply Voltages.

4

VP

Noninverting Analog Input.

6

VN

Inverting Analog Input.

7

SDN

Shutdown. Drive this pin low to shut down the device.

8

LE/HYS

Latch/Hysteresis Control. Bias with resistor or current for hysteresis; drive low to latch.

10

Q

Inverting Output. Q is at Logic low if the analog voltage at the noninverting input, VP, is greater than the

analog voltage at the inverting input, VN, if the comparator is in compare mode.

12

Q

Noninverting Output. Q is at Logic high if the analog voltage at the noninverting input, VP, is greater

than the analog voltage at the inverting input, VN, if the comparator is in compare mode.

Heat Sink Paddle VEE

The metallic back surface of the package is electrically connected to VEE. It can be left floating because

Pin 3, Pin 5, Pin 9, and Pin 11 provide adequate electrical connection. It can also be soldered to the

application board if improved thermal and/or mechanical stability is desired.

EPAD

Exposed Pad. If connected, the EPAD must be connected to VEE.

Rev. C | Page 7 of 14