CA16B2CAA 데이터 시트보기 (PDF) - Agere -> LSI Corporation

부품명

상세내역

제조사

CA16B2CAA

CA16B2CAA Datasheet PDF : 30 Pages

| |||

Advance Data Sheet

March 2001

CA16-Type 2.5 Gbits/s DWDM Transponder with

16-Channel 155 Mbits/s Multiplexer/Demultiplexer

Pin Descriptions (continued)

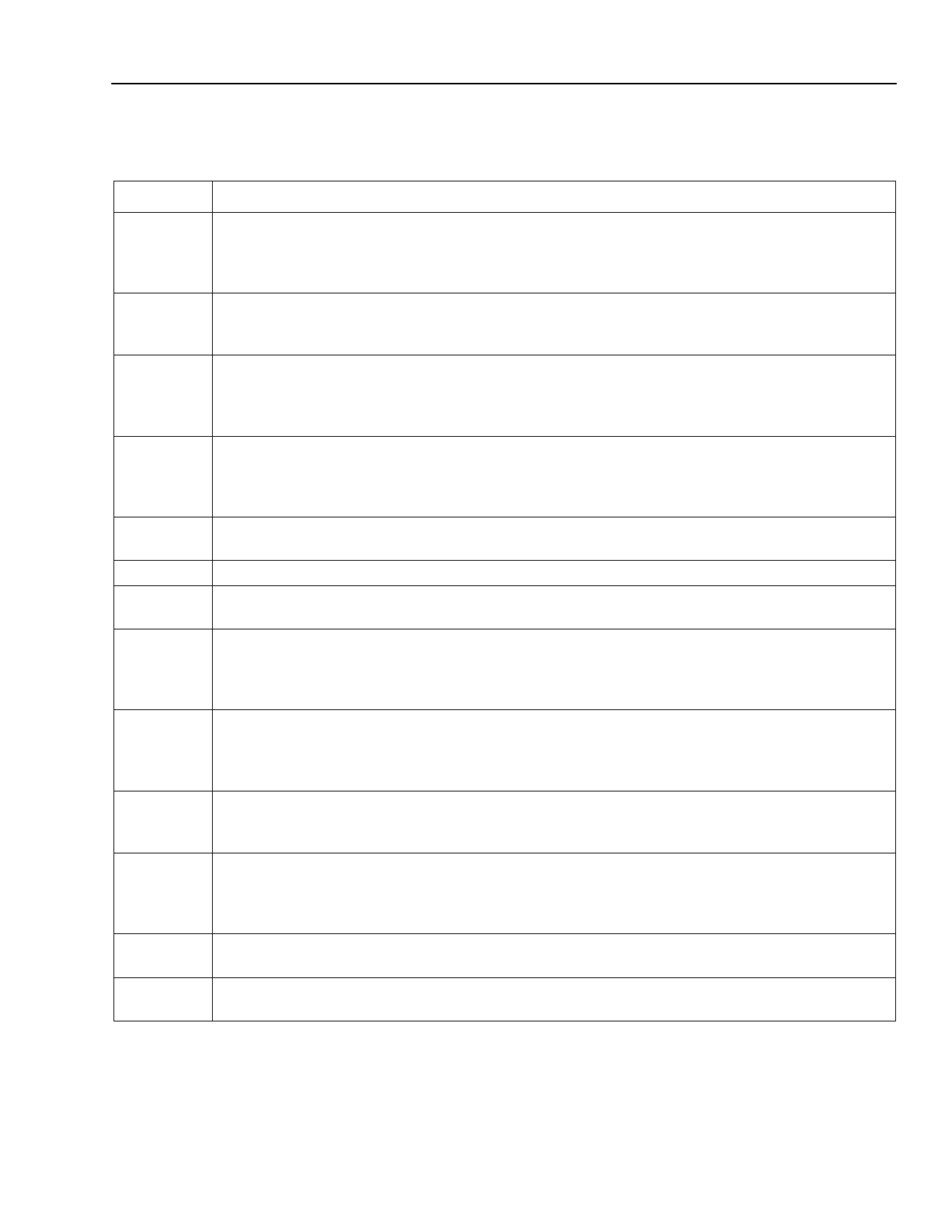

Table 3. CA16-Type Transponder Output Pin Descriptions

Pin Name

Pin Description

RxQ[0:15]P

RxQ[0:15]N

16-Bit Differential LVPECL Parallel Output Data Bus. RxQ[0:15] is the 155 Mbyte/s 16-bit output

word. RxQ15P/N is the most significant bit of the received word and is the first bit serialized.

RxQ00P/N is the least significant bit of the received word and is the last bit serialized. RxQ[0:15]P/

N is updated on the falling edge of POCLK.

POCLKP

POCLKN

FP*

SEARCH*

Differential LVPECL Parallel Output Clock. A 155 MHz nominally 50% duty cycle, byte rate out-

put clock that is aligned to the RxQ[0:15] byte serial output data. RxQ[0:15] and FP are updated on

the falling edge of POCLK.

Frame Pulse (LVPECL). Indicates frame boundaries in the received serial data stream. If framing

pattern detection is enabled (FRAMEN high and OOF), FP pulses high for one POCLK cycle when

a 32-bit sequence matching the framing pattern is detected in the received serial data. FP is

updated on the falling edge of POCLK.

A1 A2 Frame Search Output (LVTTL). A high on this output pin indicates that the frame detection

circuit is active and is searching for a new A1 A2 byte alignment. This output will be high during the

entire A1 A2 frame search. Once a new alignment is found, this signal will remain high for a mini-

mum of one 155 MHz clock period beyond the third A2 byte before it will be set low.

LOS

Loss of Signal (LVTTL). A low on this output indicates a loss of clock by the clock recovery circuit

in the optical receiver.

LSRBIAS Laser Bias Alarm (Analog). The analog bias alarm is not available on the CA16 transponders.

LSRALM Laser Degrade Alarm (5 V CMOS). This output goes to a logic 0 when the laser output power

degrades 2 dB below the nominal output power.

LPM

Laser Power Monitor (Analog). Provides an indication of the output power level from the transmit-

ter laser. This output is set at 500 mV for the nominal transmitter optical output power. If the optical

power decreases by 3 dB, this output will drop to approximately 250 mV, and if the output power

should increase by 3 dB, this output will increase to1000 mV.

PCLKP/N

Parallel Byte Clock (Differential LVPECL). A byte-rate reference clock generated by dividing the

internal 2.488 GHz serial bit clock by 16. This output is normally used to synchronize byte-wide

transfers from upstream logic into the CA16 transponder. See timing discussion for additional

details, page 18.

PHERR

Phase Error Signal (Single-Ended LVPECL). Pulses high during each PCLK cycle for which there

is a potential setup/hold timing violation between the internal byte clock and the PIC LK timing

domain. PHERR is updated on the falling edge of the PCLK outputs.

IPDMON

Receiver Photodiode Current Monitor (Analog). This output provides a current output that is a

mirror of the of the photocurrent generated by the optical receiver’s photodetector diode (APD or

PIN). A 10 kΩ resistor from pin 2 to ground provides a voltage at this output ranging from ~1 mV to

~800 mV, depending on the optical input power.

WDEA

Wavelength Deviation Alarm (5 V TTL). This output changes logic levels whenever the optical

transmitter’s wavelength deviates from the nominal wavelength by more than ±100 pm.

LOCKDET Lock Detect (LVTTL). This output goes low after the transmit side PLL has locked to the clock sig-

nal provided at the TXREFCLK input pins. LOCKDET is an asychronous output.

* Future versions of the cooled transponder will not support the frame-detect function.

Agere Systems Inc.

11