ACS8520A 데이터 시트보기 (PDF) - Semtech Corporation

부품명

상세내역

제조사

ACS8520A Datasheet PDF : 150 Pages

| |||

ACS8520A SETS

ADVANCED COMMS & SENSING

FINAL

DATASHEET

frequency to 8 kHz, the post-division frequency. PECL/LVDS/AMI Input Port Selection

(XX = “Leaky Bucket” ID for this input).

The choice of PECL or LVDS compatibility is programmed

(ii) To achieve 8 kHz, the 10 MHz input must be

divided by 1,250. So, if DivN, = 250 = (N+1)

then N must be set to 1,249. This is done by

writing 4E1 hex (1,249 decimal) to the DivN

via the cnfg_differential_inputs register. Unused PECL

differential inputs should be fixed with one input High

(VDD) and the other input Low (GND), or set in LVDS mode

and left floating, in which case one input is internally

pulled High and the other Low.

register pair Reg. 46/Reg. 47.

An AMI port supports a composite clock, consisting of a

Direct Lock Mode 155 MHz.

The max frequency allowed for phase comparison is

77.76MHz, so for the special case of a 155 MHz input set

to Direct Lock Mode, there is a divide-by-two function

automatically selected to bring the frequency down to

64 kHz AMI clock with 8 kHz boundaries marked by

deliberate violations of the AMI coding rules, as specified

in ITU recommendation G.703[6]. Departures from the

nominal pattern are detected within the ACS8520A, and

may cause reference-switching if too frequent. See

section DC Characteristics: AMI Input/Output Port, for

more details. If the AMI port is unused, the pins (I1 and I2)

within the limits of operation.

should be tied to GND.

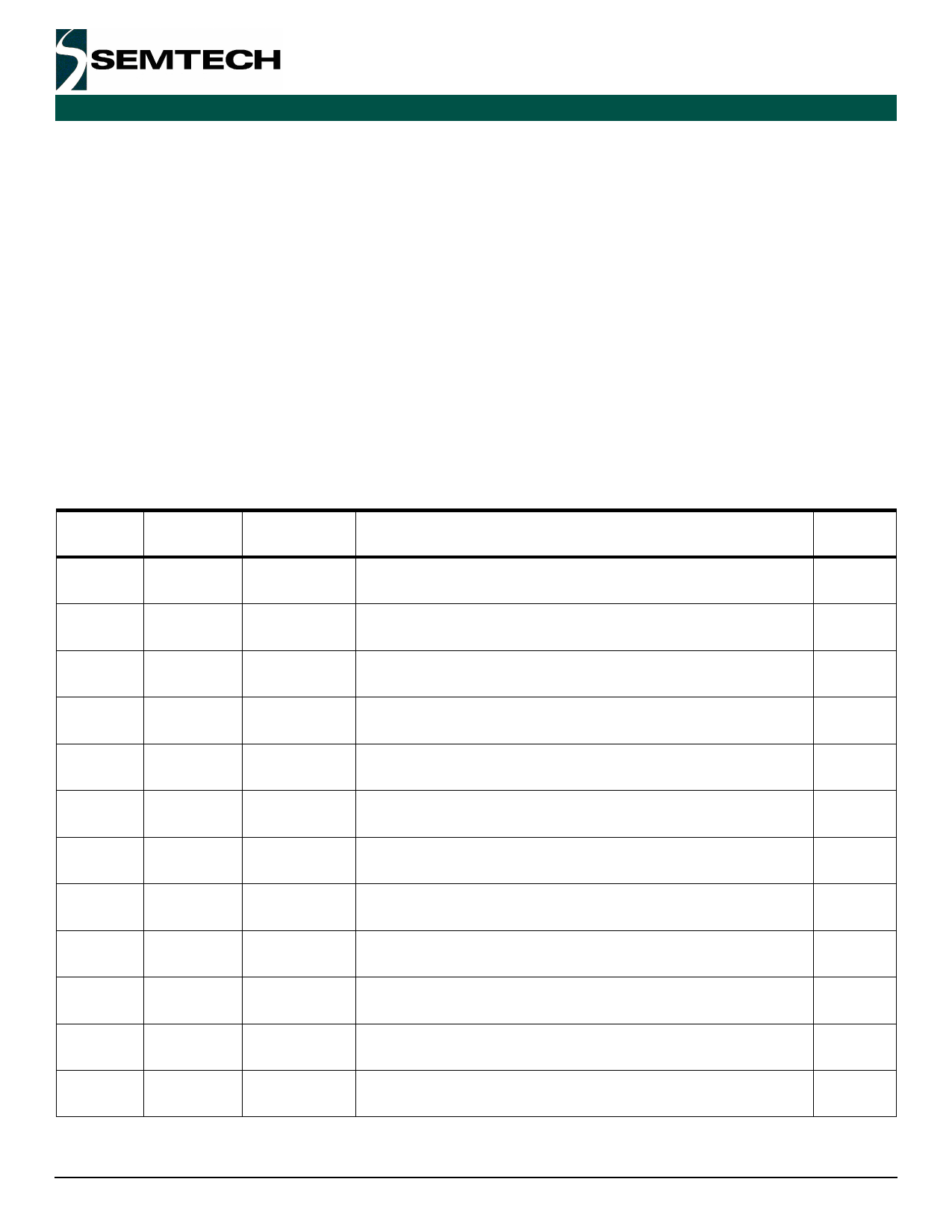

Table 4 Input Reference Source Selection and Priority Table

Port Number Channel

Number (Bin)

Input Port

Technology

Frequencies Supported

Default

Priority

I1

0001

AMI

64/8 kHz (composite clock, 64 kHz + 8 kHz)

2

Default (SONET): 64/8 kHz Default (SDH): 64/8 kHz

I2

0010

AMI

64/8 kHz (composite clock, 64 kHz + 8 kHz)

3

Default (SONET): 64/8 kHz Default (SDH): 64/8 kHz

I3

0011

TTL/CMOS

Up to 100 MHz (see Note (i))

4

Default (SONET): 8 kHz Default (SDH): 8 kHz

I4

0100

TTL/CMOS

Up to 100 MHz (see Note (i))

5

Default (SONET): 8 kHz Default (SDH): 8 kHz

I5

0101

LVDS/PECL LVDS Up to 155.52 MHz (see Note (ii))

6

default

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I6

0110

PECL/LVDS PECL Up to 155.52 MHz (see Note (ii))

7

default

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I7

0111

TTL/CMOS

Up to 100 MHz (see Note (i))

8

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I8

1000

TTL/CMOS

Up to 100 MHz (see Note (i))

9

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I9

1001

TTL/CMOS

Up to 100 MHz (see Note (i))

10

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I10

1010

TTL/CMOS

Up to 100 MHz (see Note (i))

11

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

I11

1011

TTL/CMOS

Up to 100 MHz (see Note (i)) Default (Master) (SONET): 1.544 MHz Default 12/1 (Note

(Master) (SDH): 2.048 MHz Default (Slave) 6.48 MHz

(iii))

I12

1100

TTL/CMOS

Up to 100 MHz (see Note (i))

13

Default (SONET): 1.544 MHz Default (SDH): 2.048 MHz

Revision 1.00/September 2007© Semtech Corp.

Page 11

www.semtech.com