CXD1196 데이터 시트보기 (PDF) - Sony Semiconductor

부품명

상세내역

제조사

CXD1196 Datasheet PDF : 28 Pages

| |||

CXD1196AR

Sony DSP for CD

CDL30 series

CDL35 series

CDL40 series

(48-bit slot mode)

CDL40 series

(64-bit slot mode)

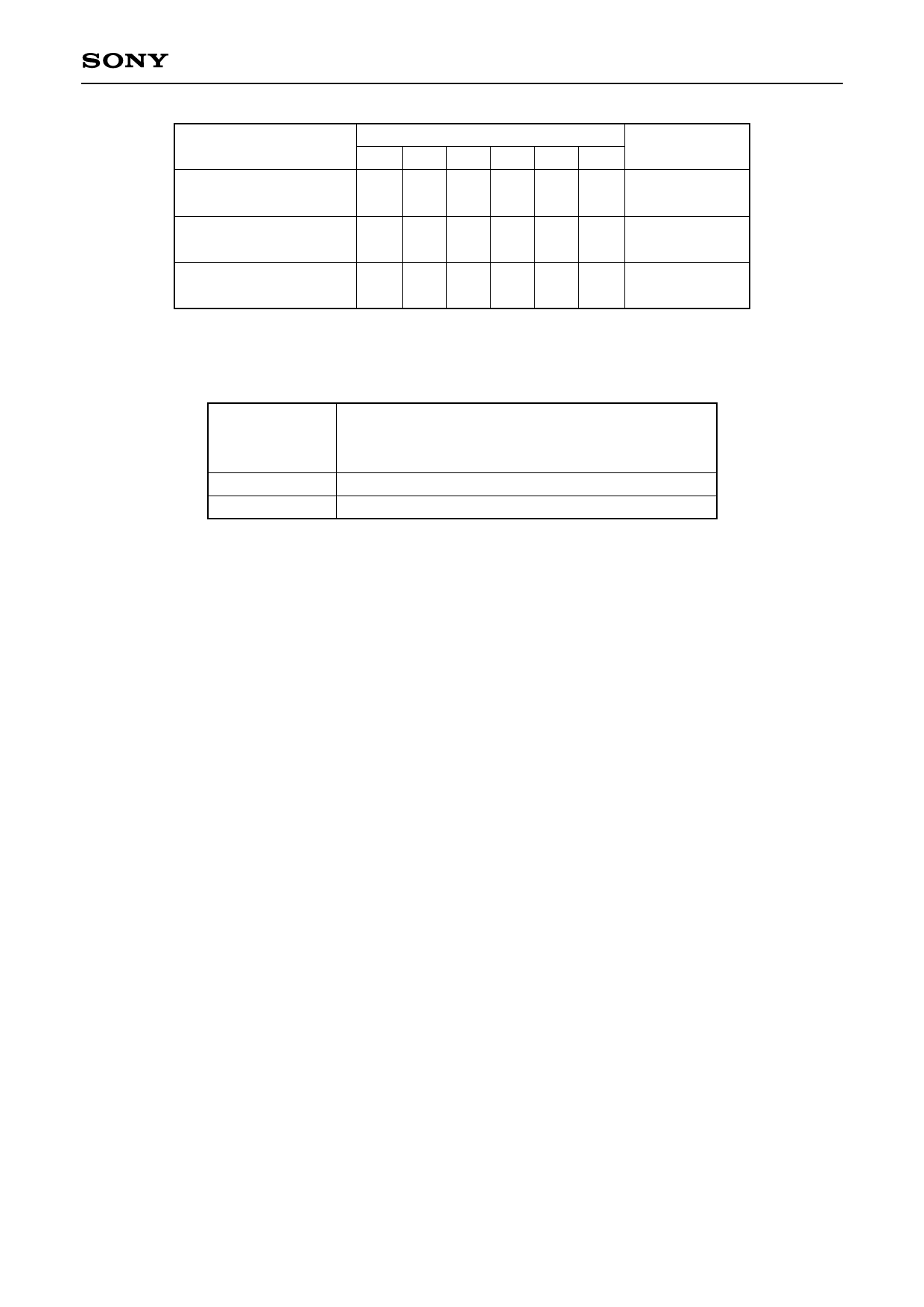

DRVIF register

bit6 bit5 bit4 bit3 bit2 bit1

L L L LHL

Timing chart

Fig. 2.1.1 (1)

L L H L H L Fig. 2.1.1 (2)

L H L H X H Fig. 2.1.1 (3)

Table 2.1.1 DRVIF Register Settings

(Note 1)

CDL30 series

CDL35 series

CDL40 series

CXD1125Q/QZ, CXD1130Q/QZ, CXD1135Q/QZ,

CXD1241Q/QZ, CXD1245Q, CXD1246Q/QZ,

CXD1247Q/QZ/R, etc.

CXD1165Q, CXD1167Q/QZ/R, etc.

CXD2500Q/QZ, etc.

2.1.3 Chip Control (CHPCTL) register

Bit7-5 RESERVED

Bit4 CHPRST (Chip Reset)

When this bit is set at ‘H’, the CXD1196AR is internally initialized. The bit setting will automatically

change to ‘L’ when the internal initialization of the CXD1196AR is completed. Therefore, there is no

need for the CPU to change the setting at ‘L’. Initialization of the CXD1196AR will be completed in

500ns after the bit has been set at ‘H’ by the CPU.

Bit3 CD-DA (CD-Digital Audio)

‘H’ : When a CD-DA disc is to be played back, this bit is set at ‘H’.

The decoder must be placed in the disabled state (DECCTL register) when this bit is set at

‘H’.

‘L’ : When a CD-ROM disc is to be played back, this bit is set at ‘L’.

Bit2 SWOPN (Sync Window Open)

‘H’ : When this bit is set at ‘H’, the window for detection of SYNC mark will open. In this case,

the SYNC protection circuit in the CXD1196AR will be disabled.

‘L’ : When this bit is set at ‘L’, the window for detection of SYNC mark will be controlled by the

SYNC protection circuit in the CXD1196AR.

Bit1 RPSTART (Repeat Correction Start)

When the DECODER is placed in the repeat correction mode, and this bit set at ‘H’, the error

correction of the current sector will begin. The bit setting will automatically change to ‘L’ when

correction begins. Therefore, there is no need for the CPU to change the setting at ‘L’.

Bit0 ADPEN (ADPCM Enable)

When the current sector is an ADPCM sector, the CPU sets this bit at ‘H’ in less than 11.5 ms after a

decoder interrupt (DECINT). When the current sector is not an ADPCM sector, the CPU changes the

bit setting at ‘L’ in less than 11.5 ms after a decoder interrupt (DECINT).

—18—