ESDALC6V1W5(2002) 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

ESDALC6V1W5 Datasheet PDF : 9 Pages

| |||

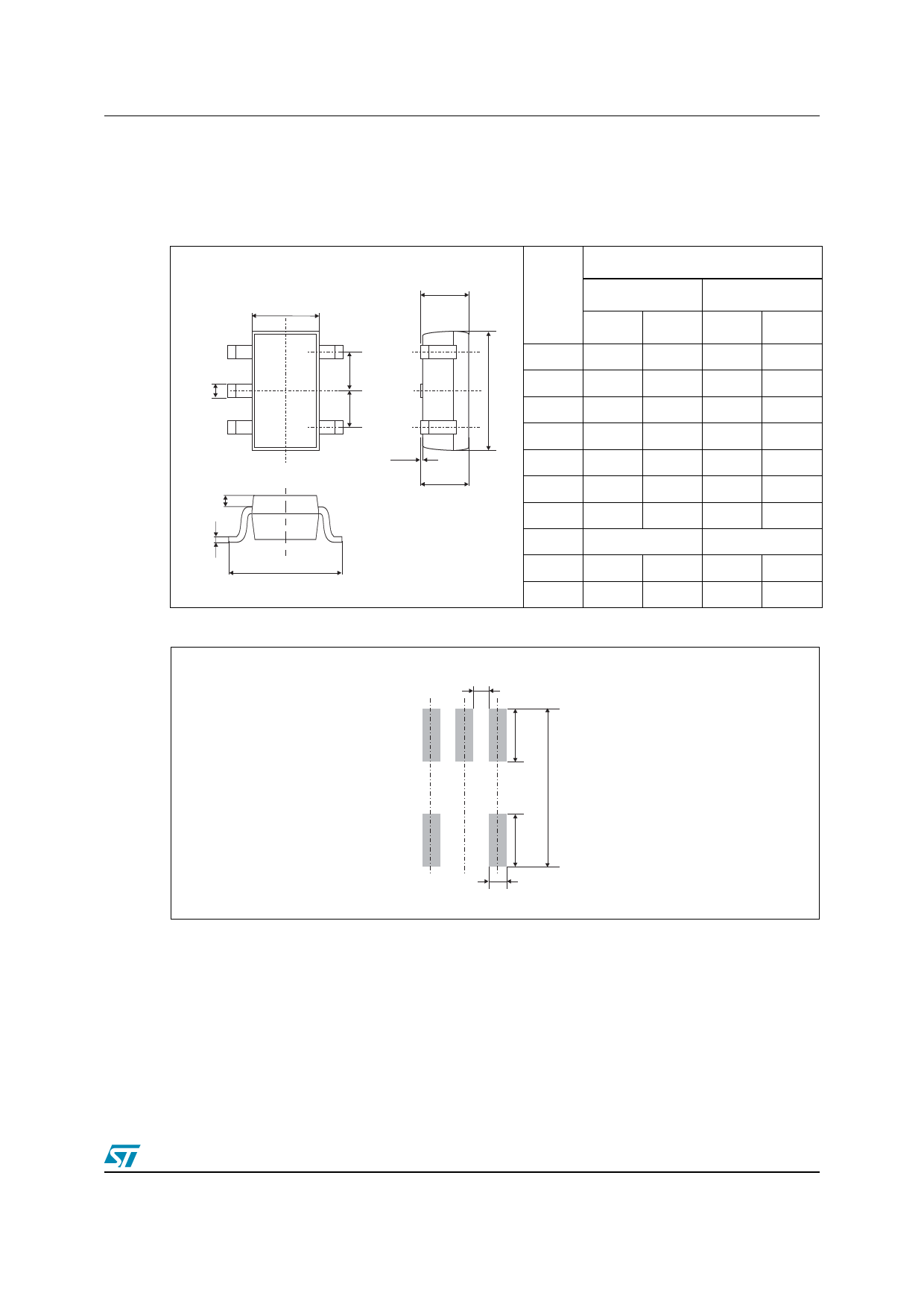

Fig. A2: ESD test board

TEST BOARD

V((ii//oo) )

ESDALC6V1W5

Fig. A3: ESD test configuration

I/O1, I/O2, I/O3 or I/O4

± 8kV

ESD Contact

discharge

V(i/o)

B2

The measurements done here after show very clearly (Fig. A4) the high efficiency of the ESD protection:

the clamping voltage V(i/o) becomes very close to +VBR (positive way, Fig. A4a) and -VBR (negative way,

Fig. A4b).

Fig. A4: Remaining voltage during ESD surge

V(i/o)

V(i/o)

a: Response in the positive way

b: Response in the negative way

5/9