MF6 데이터 시트보기 (PDF) - Unspecified

부품명

상세내역

제조사

MF6 Datasheet PDF : 20 Pages

| |||

1.0 MF6 Application Hints (Continued)

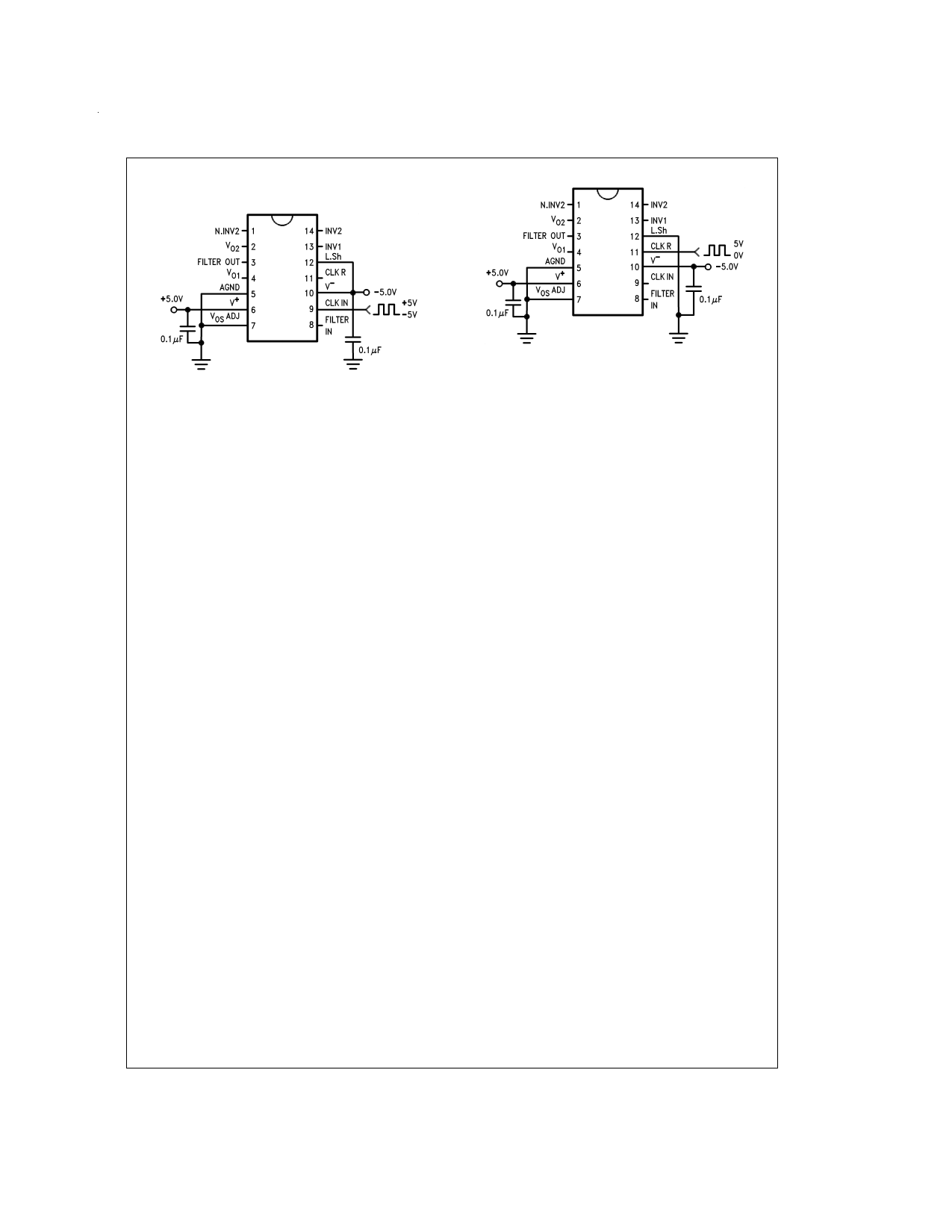

DS005065-3

FIGURE 2. Dual Supply Operation

MF6 Driven with CMOS Logic Level Clock

(VIH ≥ 0.8 VCC and VIL ≤ 0.2 VCC where VCC = V+ − V−)

DS005065-4

FIGURE 3. Dual Supply Operation

MF6 Driven with TTL Logic Level Clock

11

www.national.com