ADSP-BF518KSWZ-ENG 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADSP-BF518KSWZ-ENG Datasheet PDF : 62 Pages

| |||

Preliminary Technical Data

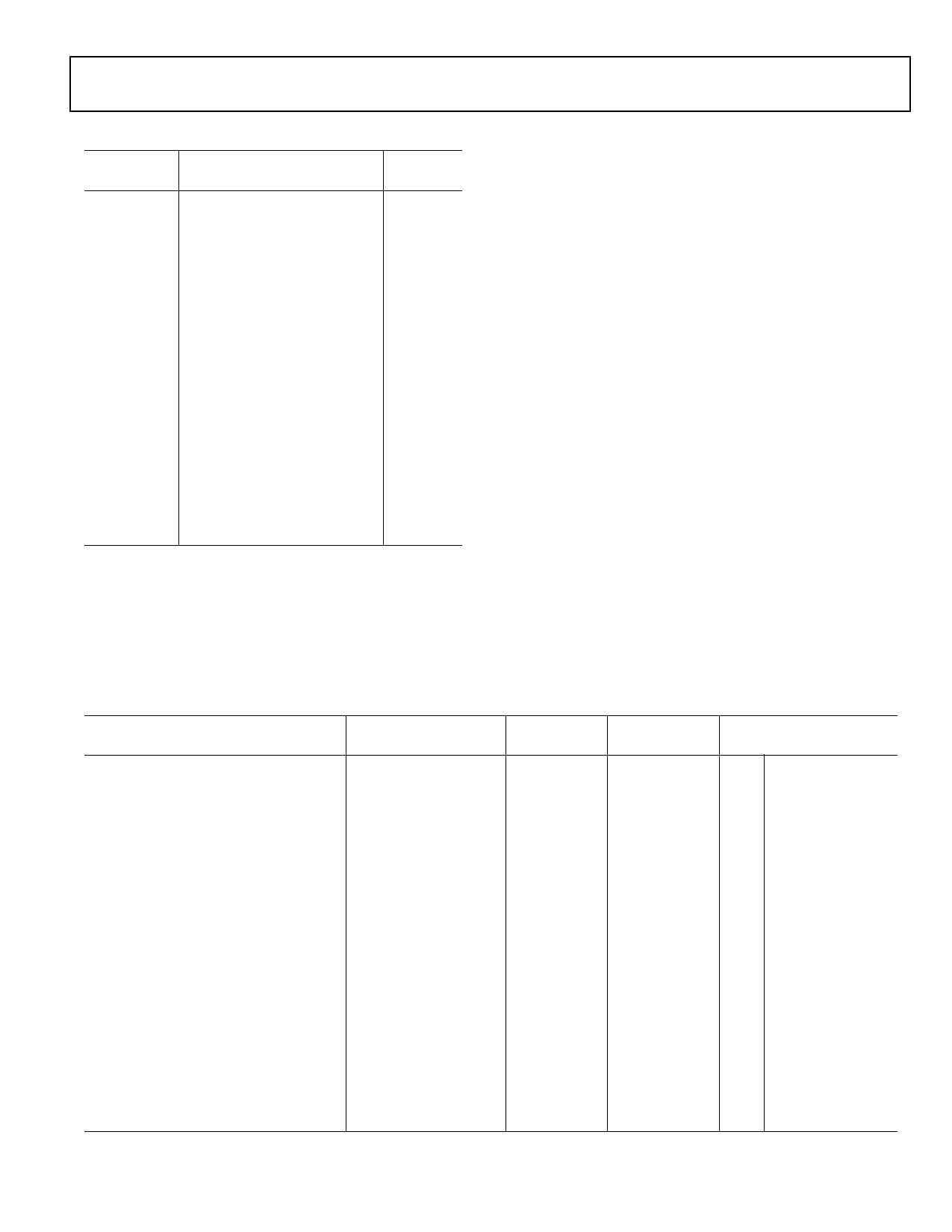

Table 2. Core Event Controller (CEC)

Priority

(0 is Highest) Event Class

0

Emulation/Test Control

1

Reset

2

Nonmaskable Interrupt

3

Exception

4

Reserved

5

Hardware Error

6

Core Timer

7

General-Purpose Interrupt 7

8

General-Purpose Interrupt 8

9

General-Purpose Interrupt 9

10

General-Purpose Interrupt 10

11

General-Purpose Interrupt 11

12

General-Purpose Interrupt 12

13

General-Purpose Interrupt 13

14

General-Purpose Interrupt 14

15

General-Purpose Interrupt 15

EVT Entry

EMU

RST

NMI

EVX

—

IVHW

IVTMR

IVG7

IVG8

IVG9

IVG10

IVG11

IVG12

IVG13

IVG14

IVG15

System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and rout-

ing of events from the many peripheral interrupt sources to the

prioritized general-purpose interrupt inputs of the CEC.

Although the processors provide a default mapping, the user

can alter the mappings and priorities of interrupt events by writ-

Table 3. Peripheral Interrupt Assignment

Peripheral Interrupt Event

PLL Wakeup Interrupt

DMA Error 0 (generic)

DMAR0 Block Interrupt

DMAR1 Block Interrupt

DMAR0 Overflow Error

DMAR1 Overflow Error

PPI Error

MAC Status

SPORT0 Status

SPORT1 Status

PTP Error Interrupt

Reserved

UART0 Status

UART1 Status

RTC

DMA 0 Channel (PPI)

DMA 3 Channel (SPORT0 RX)

General Purpose

Interrupt (at Reset)

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG8

IVG8

IVG9

ADSP-BF512/BF514/BF516/BF518 (F)

ing the appropriate values into the interrupt assignment

registers (SIC_IARx). Table 3 describes the inputs into the SIC

and the default mappings into the CEC.

Event Control

The ADSP-BF512/BF514/BF516/BF518(F) processors provide a

very flexible mechanism to control the processing of events. In

the CEC, three registers are used to coordinate and control

events. Each register is 16 bits wide.

• CEC interrupt latch register (ILAT) – Indicates when

events have been latched. The appropriate bit is set when

the processor has latched the event and cleared when the

event has been accepted into the system. This register is

updated automatically by the controller, but it may be writ-

ten only when its corresponding IMASK bit is cleared.

• CEC interrupt mask register (IMASK) – Controls the

masking and unmasking of individual events. When a bit is

set in the IMASK register, that event is unmasked and is

processed by the CEC when asserted. A cleared bit in the

IMASK register masks the event, preventing the processor

from servicing the event even though the event may be

latched in the ILAT register. This register may be read or

written while in supervisor mode. (Note that general-pur-

pose interrupts can be globally enabled and disabled with

the STI and CLI instructions, respectively.)

• CEC interrupt pending register (IPEND) – The IPEND

register keeps track of all nested events. A set bit in the

IPEND register indicates the event is currently active or

nested at some level. This register is updated automatically

by the controller but may be read while in supervisor mode.

Peripheral

Interrupt ID

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Default Core

Interrupt ID

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

2

SIC Registers

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR0 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR1 IMASK0 and ISR0

IAR2 IMASK0 and ISR0

Rev. PrE | Page 7 of 62 | March 2009