MSM80C88A-10GS-K 데이터 시트보기 (PDF) - Oki Electric Industry

부품명

상세내역

제조사

MSM80C88A-10GS-K Datasheet PDF : 37 Pages

| |||

¡ Semiconductor

MSM80C88A-10RS/GS/JS

PIN DESCRIPTION

AD0 - AD7

ADDRESS DATA BUS: Input/Output

These lines are the multiplexed address and data bus.

These are the address bus at T1 cycle and the data bus at T2, T3, TW and T4 cycle.

T2, T3, TW and T4 cycle.

These lines are high impedance during interrupt acknowledge and hold acknowledge.

A8 - A15

ADDRESS BUS: Output

These lines are the address bus bits 8 thru 15 at all cycles.

These lines do not have to be latched by an ALE signal.

These lines are high impedance during interrupt acknowledge and hold acknowledge.

A16/S3, A17/S4, A18/S5, A19/S6

ADDRES/STATUS : Output

These are the four most significant address as at the T1, cycle.

Accessing I/O port address, these are low at T1 Cycle.

These lines are Status lines at the T2, T3, TW and T4 Cycles.

S5 indicates interrupt enable Flag.

S3 and S4 are encoded as shown below.

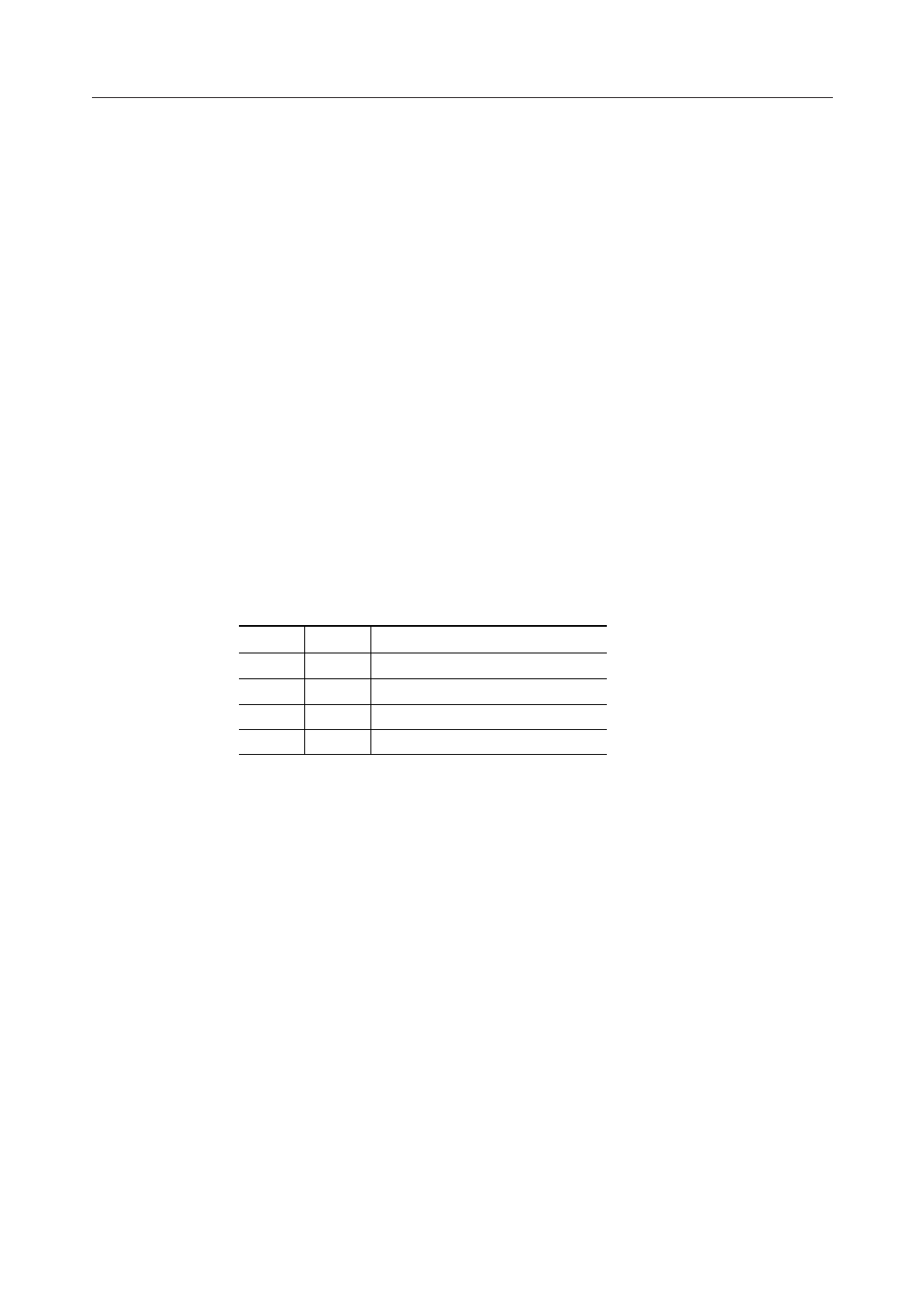

S3

S4

0

0

1

0

0

1

1

1

Characteristics

Alternate Data

Stack

Code or None

Data

These lines are high impedance during hold acknowledge.

RD

READ: Output

This line indicates that CPU is in a memory or I/O read cycle.

This line is the read strobe signal when CPU reads data from a memory or I/O device. This

line is active low.

This line is high impedance during hold acknowledge.

READY

READY:Input

This line indicates to the CPU that the addressed memory or I/O device is ready to read or

write.

This line is active high. If the setup and hold time are out of specification, an illegal operation

will occur.

INTR

INTERRUPT REQUEST: Input

This line is the level triggered interrupt request signal which is sampled during the last clock

cycle of instruction and string manipulations.

It can be internally masked by software.

This signal is active high and internally synchronized.

15/37