LC66354C 데이터 시트보기 (PDF) - SANYO -> Panasonic

부품명

상세내역

제조사

LC66354C Datasheet PDF : 21 Pages

| |||

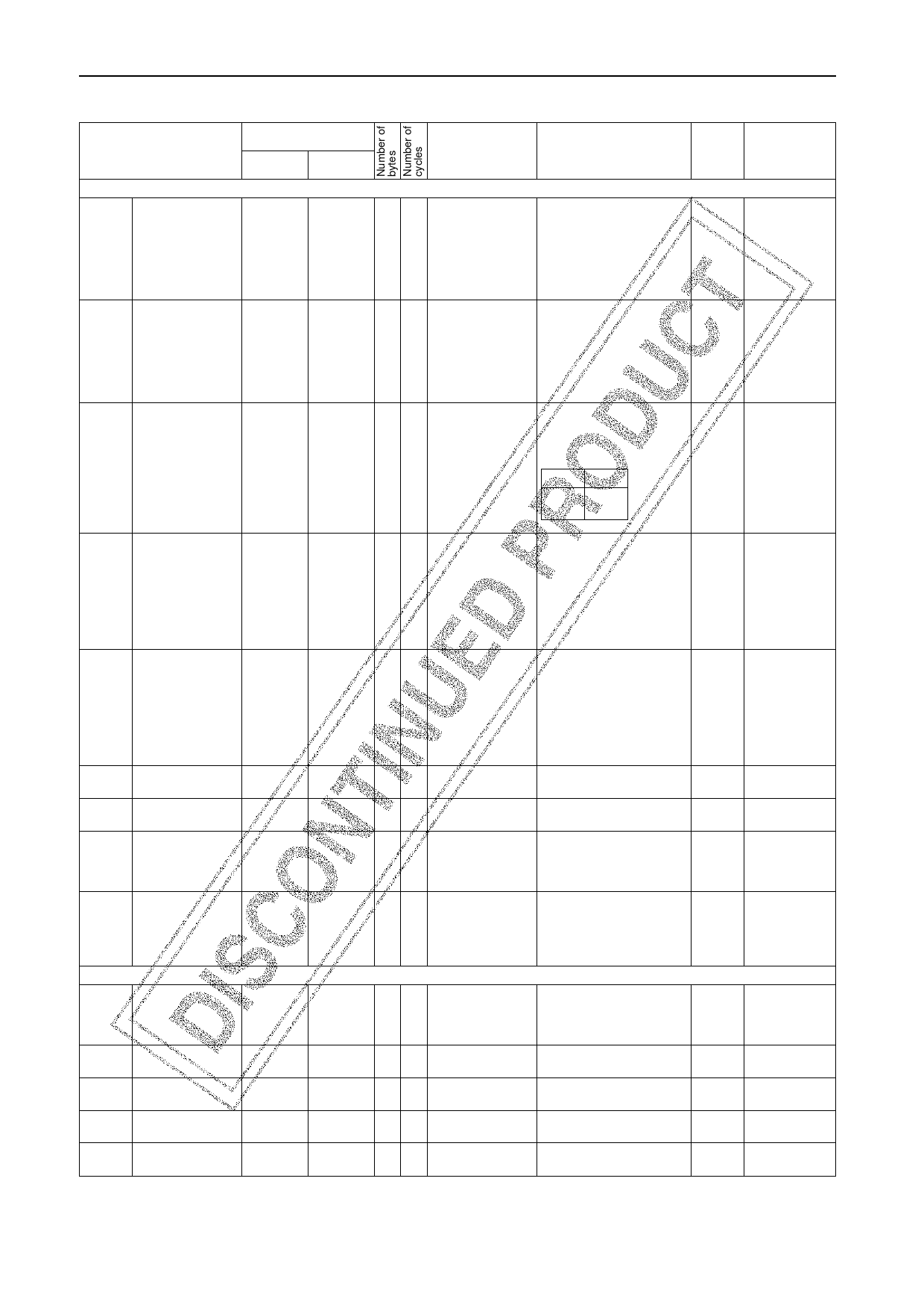

LC66354C, 66356C, 66358C

Continued from preceding page.

Mnemonic

[Load and store instructions]

Instruction code

D7 D6 D5 D4 D3 D2 D1 D0

LA reg, I Load AC from M (reg) 0 1 0 0

then increment reg

1 0 t0 1

1

LA reg, D Load AC from M (reg) 0 1 0 1

then decrement reg

1 0 t0 1

1

XA reg Exchange AC with

M (reg)

0 1 0 0 1 1 t0 0 1

Operation

Description

Affected

status

bits

Note

Load the contents of M (reg)

into AC. (The reg is either HL

AC ← [M (reg)]

or XY.) Then increment the

2 DPL ← (DPL) + 1

contents of either DPL or DPY. ZF

or DPY ← (DPY) + 1 The relationship between t0

and reg is the same as that

for the LA reg instruction.

Load the contents of M (reg)

into AC. (The reg is either HL

AC ← [M (reg)]

or XY.) Then decrement the

2 DPL ← (DPL) – 1

contents of either DPL or DPY. ZF

or DPY ← (DPY) – 1 The relationship between t0

and reg is the same as that

for the LA reg instruction.

1 (AC) ↔ [M (reg)]

Exchange the contents of

M (reg) and AC.

The reg is either HL or XY

depending on t0.

reg

T0

HL

0

XY

1

ZF is set

according to the

result of

incrementing

DPL or DPY.

ZF is set

according to the

result of

decrementing

DPL or DPY.

Exchange AC with

XA reg, I M (reg) then

increment reg

0 1 0 0 1 1 t0 1 1

Exchange AC with

XA reg, D M (reg) then

decrement reg

0 1 0 1 1 1 t0 1 1

Exchange AC with

XADR i8 M direct

Load E & AC with

LEAI i8 immediate data

1100 1000

I7 I6 I5 I4 I3 I2 I1 I0 2

1100 0110

I7 I6 I5 I4 I3 I2 I1 I0 2

RTBL

Read table data from

program ROM

0101 1010 1

Read table data from

RTBLP program ROM then 0 1 0 1 1 0 0 0 1

output to P4, 5

[Data pointer manipulation instructions]

LDZ i4

Load DPH with zero

and DPL with

immediate data

0 1 1 0 I3 I2 I1 I0 1

respectively

LHI i4

Load DPH with

immediate data

1100 1111

0 0 0 0 I3 I2 I1 I0 2

LLI i4

Load DPL with

immediate data

1100 1111

0 0 0 1 I3 I2 I1 I0 2

LHLI i8

Load DPH, DPL with 1 1 0 0 0 0 0 0

immediate data

I7 I6 I5 I4 I3 I2 I1 I0

2

LXYI i8

Load DPX, DPY with 1 1 0 0 0 0 0 0

immediate data

I7 I6 I5 I4 I3 I2 I1 I0

2

Exchange the contents of

M (reg) and AC. (The reg is

either HL or XY.) Then

(AC) ↔ [M (reg)]

increment the contents of

2

DPL ← (DPL) + 1

or DPY ← (DPY) + 1

either DPL or DPY. The

relationship between t0 and

ZF

reg is the same as that for

the XA reg instruction.

Exchange the contents of

M (reg) and AC. (The reg is

either HL or XY.) Then

(AC) ↔ [M (reg)]

decrement the contents of

2

DPL ← (DPL) – 1

or DPY ← (DPY) – 1

either DPL or DPY. The

relationship between t0 and

ZF

reg is the same as that for

the XA reg instruction.

2 (AC) ↔ [M (i8)]

Exchange the contents of AC

and M (i8).

2

E ← I7 I6 I5 I4

AC ← I3 I2 I1 I0

Load the immediate data i8

into E, AC.

Load into E, AC the ROM data

2

E, AC ←

at the location determined by

[ROM (PCh, E, AC)] replacing the lower 8 bits of

the PC with E, AC.

Output from ports 4 and 5 the

ROM data at the location

2 Port 4, 5 ←

determined by replacing the

[ROM (PCh, E, AC)] lower 8 bits of the PC with

E, AC.

1

DPH ← 0

DPL ← I3 I2 I1 I0

2 DPH ← I3 I2 I1 I0

2 DPL ← I3 I2 I1 I0

2

DPH ← I7 I6 I5 I4

DPL ← I3 I2 I1 I0

2

DPX ← I7 I6 I5 I4

DPY ← I3 I2 I1 I0

Load zero into DPH and the

immediate data i4 into DPL.

Load the immediate data i4

into DPH.

Load the immediate data i4

into DPL.

Load the immediate data into

DLH, DPL.

Load the immediate data into

DLX, DPY.

ZF is set

according to the

result of

incrementing

DPL or DPY.

ZF is set

according to the

result of

decrementing

DPL or DPY.

Continued on next page.

No. 5484-16/21