LC66354C 데이터 시트보기 (PDF) - SANYO -> Panasonic

부품명

상세내역

제조사

LC66354C Datasheet PDF : 21 Pages

| |||

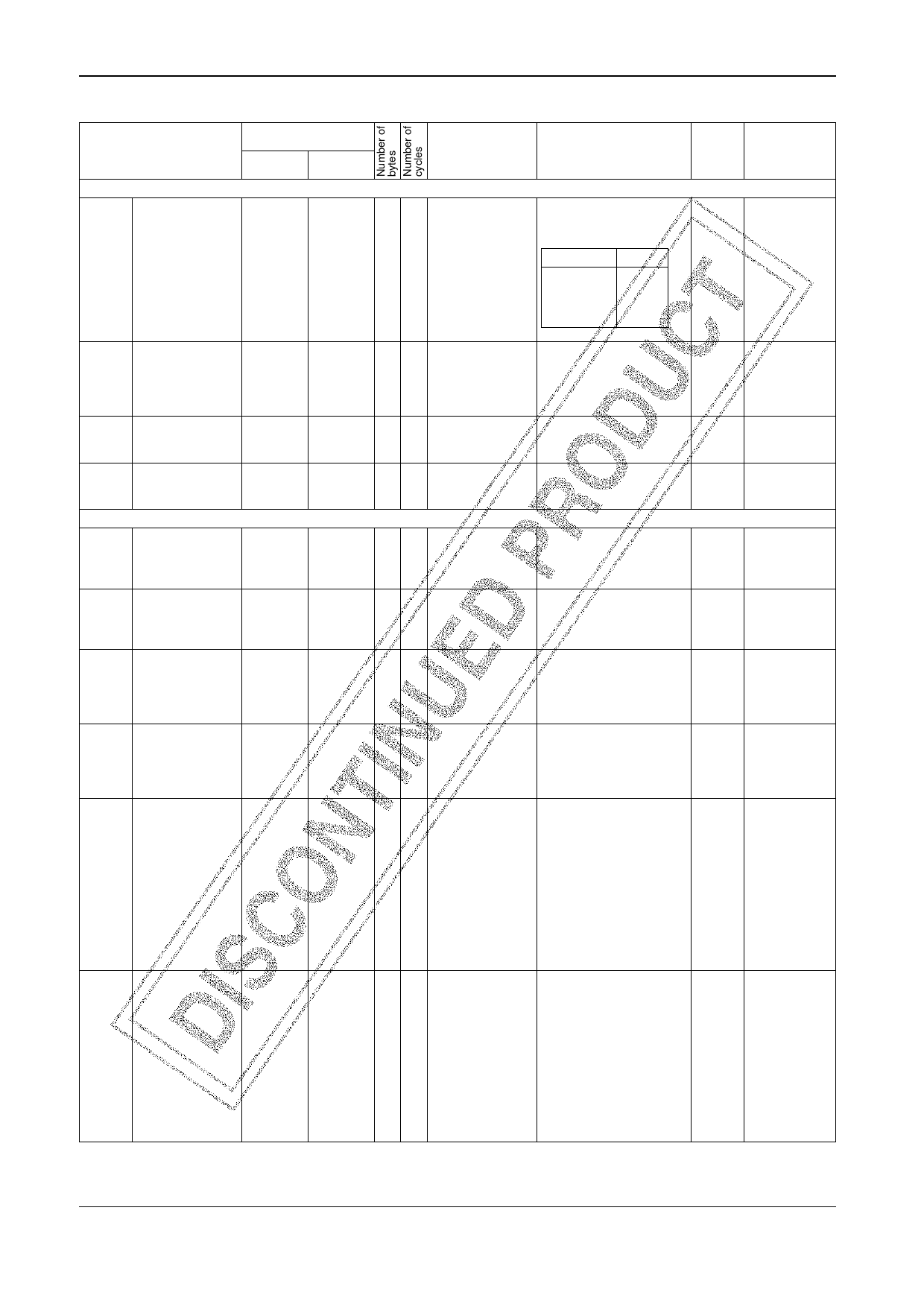

LC66354C, 66356C, 66358C

Continued from preceding page.

Mnemonic

Instruction code

D7 D6 D5 D4 D3 D2 D1 D0

[Jump and subroutine instructions]

Operation

PUSH

reg

1100 1111

M2 (SP) ← (reg)

Push reg on M2 (SP) 1 1 1 1 1 i1 i0 0 2 2 SP ← (SP) – 2

Description

Affected

status

bits

Store the contents of reg in

M2 (SP). Subtract 2 from SP

after the store.

reg

HL

XY

AE

Illegal value

i1 i0

00

01

10

11

Note

POP

reg

Pop reg off M2 (SP) 1 1 0 0 1 1 1 1 2

1 1 1 0 1 i1 i0 0

RT

Return from

subroutine

0001 1100 1

RTI

Return from interrupt 0 0 0 1 1 1 0 1 1

routine

[Branch instructions]

BAt2

addr

Branch on AC bit

1 1 0 1 0 0 t1 t0

P7 P6 P5 P4 P3 P2 P1 P0

2

BNAt2

addr

Branch on no AC bit

1 0 0 1 0 0 t1 t0

P7 P6 P5 P4 P3 P2 P1 P0

2

BMt2

addr

Branch on M bit

1 1 0 1 0 1 t1 t0 2

P7 P6 P5 P4 P3 P2 P1 P0

BNMt2 Branch on no M bit 1 0 0 1 0 1 t1 t0 2

addr

P7 P6 P5 P4 P3 P2 P1 P0

BPt2

addr

Branch on Port bit

1 1 0 1 1 0 t1 t0

P7 P6 P5 P4 P3 P2 P1 P0

2

BNPt2

addr

Branch on no Port bit

1001

P7 P6 P5 P4

1 0 t1 t0

P3 P2 P1 P0

2

2

SP ← (SP) + 2

reg ← [M2 (SP)]

Add 2 to SP and then load the

contents of M2(SP) into reg.

The relation between i1i0 and

reg is the same as that for the

PUSH reg instruction.

2 SP ← (SP) + 4

PC ← [M4 (SP)]

Return from a subroutine or

interrupt handling routine. ZF

and CF are not restored.

SP ← (SP) + 4

Return from a subroutine or

2 PC ← [M4 (SP)]

interrupt handling routine. ZF ZF, CF

CF, ZF ← [M4 (SP)] and CF are restored.

PC7 to 0 ←

2

P7 P6 P5 P4

P3 P2 P1 P0

if (AC, t2) = 1

PC7 to 0 ←

2

P7 P6 P5 P4

P3 P2 P1 P0

if (AC, t2) = 0

PC7 to 0 ←

P7 P6 P5 P4

2

P3 P2 P1 P0

if [M (HL),t2]

=1

PC7 to 0 ←

P7 P6 P5 P4

2

P3 P2 P1 P0

if [M (HL),t2]

=0

Branch to the location in the

same page specified by P7 to

P0 if the bit in AC specified by

the immediate data t1 t0 is one.

Branch to the location in the

same page specified by P7 to

P0 if the bit in AC specified by

the immediate data t1 t0 is zero.

Branch to the location in the

same page specified by P7 to

P0 if the bit in M (HL) specified

by the immediate data t1 t0

is one.

Branch to the location in the

same page specified by P7 to

P0 if the bit in M (HL) specified

by the immediate data t1 t0

is zero.

PC7 to 0 ←

P7 P6 P5 P4

2

P3 P2 P1 P0

if [P (DPL), t2]

=1

Branch to the location in the

same page specified by P7 to

P0 if the bit in port (DPL)

specified by the immediate

data t1 t0 is one.

PC7 to 0 ←

P7 P6 P5 P4

2

P3 P2 P1 P0

if [P (DPL), t2]

=0

Branch to the location in the

same page specified by P7 to

P0 if the bit in port (DPL)

specified by the immediate

data t1 t0 is zero.

Internal control

registers can also

be tested by

executing this

instruction

immediately after

a BANK

instruction.

However, this is

limited to

registers that can

be read out.

Internal control

registers can also

be tested by

executing this

instruction

immediately after

a BANK

instruction.

However, this is

limited to

registers that can

be read out.

Continued on next page.

No. 5484-18/21