ADSP-BF538 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADSP-BF538 Datasheet PDF : 56 Pages

| |||

Preliminary Technical Data

DMA channels, one for transmit and one for receive. These

DMA channels have lower default priority than most DMA

channels because of their relatively low service rates.

The UART port's baud rate, serial data format, error code gen-

eration and status, and interrupts are programmable:

• Supporting bit rates ranging from (fSCLK/ 1,048,576) to

(fSCLK/16) bits per second.

• Supporting data formats from 7 to12 bits per frame.

• Both transmit and receive operations can be configured to

generate maskable interrupts to the processor.

The UART port’s clock rate is calculated as:

UART Clock Rate

=

------------------f-S---C---L---K-------------------

16 × UART_Divisor

Where the 16-bit UART_Divisor comes from the UARTx_DLH

register (most significant 8 bits) and UARTx_DLL register (least

significant 8 bits).

In conjunction with the general-purpose timer functions, auto-

baud detection is supported.

The capabilities of the UARTs are further extended with sup-

port for the Infrared Data Association (IrDA®) Serial Infrared

Physical Layer Link Specification (SIR) protocol.

GENERAL-PURPOSE PORTS

The ADSP-BF538/ADSP-BF538F processors have up to 54 gen-

eral-purpose I/O pins that are multiplexed with other

peripherals. They are arranged into ports C, D, E, and F as

shown in Table 4.

The general-purpose I/O pins may be individually controlled by

manipulation of the control and status registers. These pins may

be polled to determine their status.

• GPIO direction control register – Specifies the direction of

each individual GPIOx pin as input or output.

• GPIO control and status registers – The processor employs

a “write one to modify” mechanism that allows any combi-

nation of individual GPIO to be modified in a single

instruction, without affecting the level of any other GPIO.

Four control registers and a data register are provided for

each GPIO port. One register is written in order to set

GPIO values, one register is written in order to clear GPIO

values, one register is written in order to toggle GPIO val-

ues, and one register is written in order to specify a GPIO

input or output. Reading the GPIO Data allows software to

determine the state of the input GPIO pins.

In addition to the GPIO function described above, the 16 port F

pins can be individually configured to generate interrupts.

• Flag interrupt mask registers – The two Flag interrupt

mask registers allow each individual PFx pin to function as

an interrupt to the processor. similar to the two flag control

registers that are used to set and clear individual flag values,

one flag interrupt mask register sets bits to enable interrupt

function, and the other flag interrupt mask register clears

bits to disable interrupt function. PFx pins defined as

ADSP-BF538/ADSP-BF538F

inputs can be configured to generate hardware interrupts,

while output PFx pins can be triggered by software

interrupts.

• Flag interrupt sensitivity registers – The two flag interrupt

sensitivity registers specify whether individual PFx pins are

level- or edge-sensitive and specify—if edge-sensitive—

whether just the rising edge or both the rising and falling

edges of the signal are significant. One register selects the

type of sensitivity, and one register selects which edges are

significant for edge-sensitivity.

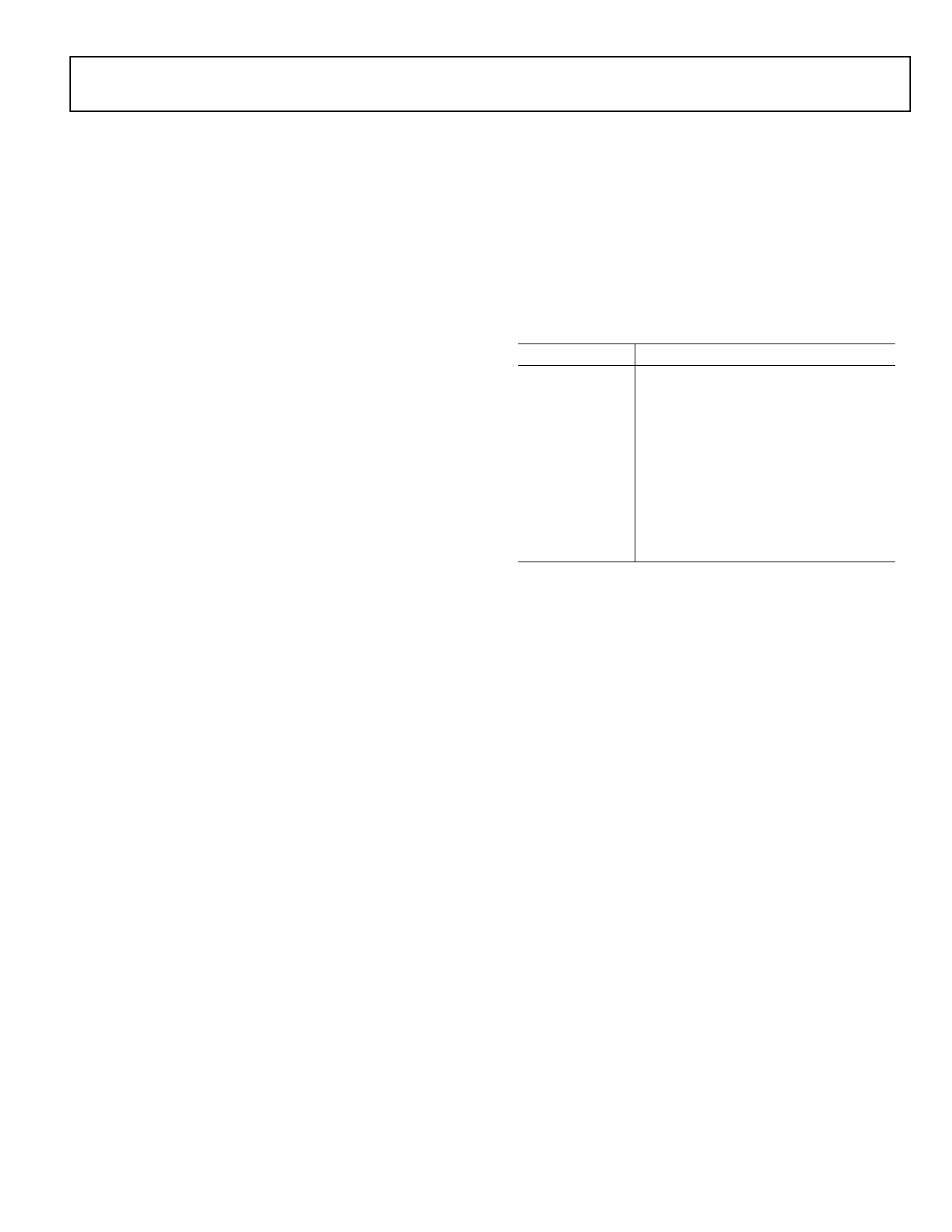

Table 4. GPIO Ports

Peripheral

PPI

SPORT2

SPORT3

SPI1

SPI2

UART1

UART2

CAN

GPIO

Alternate GPIO Port Function

GPIO Port F15–0

GPIO Port E7–0

GPIO Port E15–8

GPIO Port D4–0

GPIO Port D9–5

GPIO Port D11–10

GPIO Port D13–12

GPIO Port C1–0

GPIO Port C9–4

PARALLEL PERIPHERAL INTERFACE

The ADSP-BF538/ADSP-BF538F processors provide a parallel

peripheral interface (PPI) that can connect directly to parallel

A/D and D/A converters, video encoders and decoders, and

other general-purpose peripherals. The PPI consists of a dedi-

cated input clock pin, up to 3 frame synchronization pins, and

at up to 16 data pins. The input clock supports parallel data rates

at up to fSCLK/2 MHz, and the synchronization signals can be con-

figured as either inputs or outputs.

The PPI supports a variety of general-purpose and ITU-R 656

modes of operation. In general-purpose mode, the PPI provides

half-duplex, bi-directional data transfer with up to 16 bits of

data. Up to 3 frame synchronization signals are also provided.

In ITU-R 656 mode, the PPI provides half-duplex, bi-direc-

tional transfer of 8- or 10-bit video data. Additionally, on-chip

decode of embedded start-of-line (SOL) and start-of-field (SOF)

preamble packets is supported.

General-Purpose Mode Descriptions

The general-purpose modes of the PPI are intended to suit a

wide variety of data capture and transmission applications.

Three distinct submodes are supported:

• Input mode – frame syncs and data are inputs into the PPI.

• Frame capture mode – frame syncs are outputs from the

PPI, but data are inputs.

• Output mode – frame syncs and data are outputs from the

PPI.

Rev. PrD | Page 11 of 56 | May 2006