MT28F002B3 데이터 시트보기 (PDF) - Micron Technology

부품명

상세내역

제조사

MT28F002B3 Datasheet PDF : 31 Pages

| |||

2Mb

SMART 3 BOOT BLOCK FLASH MEMORY

COMMAND SET

To simplify writing of the memory blocks, the

MT28F002B3 and MT28F200B3 incorporate an ISM

that controls all internal algorithms for the WRITE and

ERASE cycles. An 8-bit command set is used to control

the device. Details on how to sequence commands are

provided in the Command Execution section. Table 1

lists the valid commands.

ISM STATUS REGISTER

The 8-bit ISM status register (see Table 2) is polled to

check for WRITE or ERASE completion or any related

errors. During or following a WRITE, ERASE or ERASE

SUSPEND, a READ operation will output the status

register contents on DQ0-DQ7 without prior com-

mand. While the status register contents are read, the

outputs will not be updated if there is a change in the

ISM status unless OE# or CE# is toggled. If the device is

not in the write, erase, erase suspend or status register

read mode, READ STATUS REGISTER (70H) can be

issued to view the status register contents.

All of the defined bits are set by the ISM, but only the

ISM and erase suspend status bits are reset by the ISM.

The erase, write and VPP status bits must be cleared

using CLEAR STATUS REGISTER. If the VPP status bit

(SR3) is set, the CEL will not allow further WRITE or

ERASE operations until the status register is cleared.

This allows the user to choose when to poll and clear

the status register. For example, the host system may

perform multiple BYTE WRITE operations before check-

ing the status register instead of checking after each

individual WRITE. Asserting the RP# signal or powering

down the device will also clear the status register.

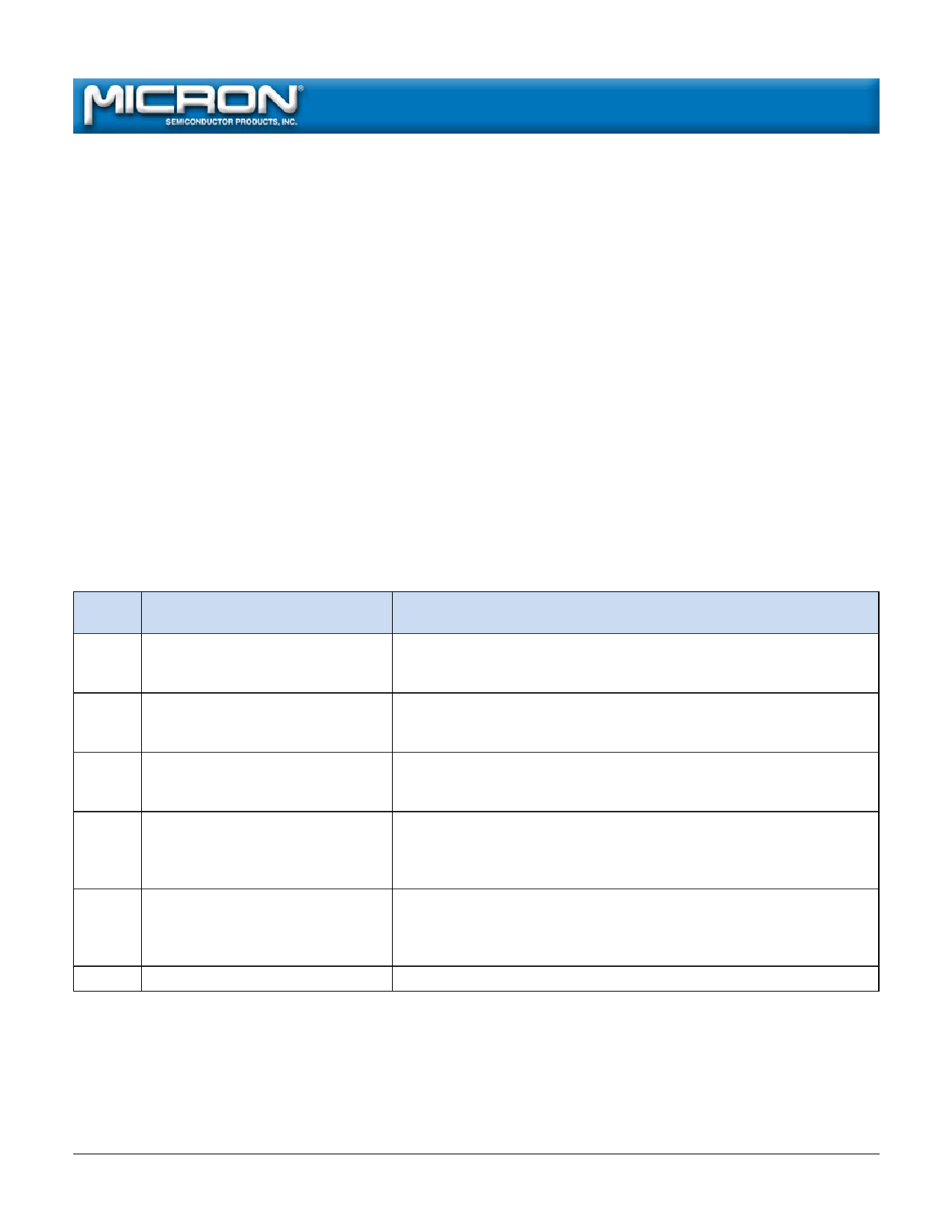

STATUS

BIT #

SR7

SR6

SR5

SR4

SR3

STATUS REGISTER BIT

ISM STATUS

1 = Ready

0 = Busy

ERASE SUSPEND STATUS

1 = ERASE suspended

0 = ERASE in progress/completed

ERASE STATUS

1 = BLOCK ERASE error

0 = Successful BLOCK ERASE

WRITE STATUS

1 = WORD/BYTE WRITE error

0 = Successful WORD/

BYTE WRITE

VPP STATUS

1 = No VPP voltage detected

0 = VPP present

SR0-2 RESERVED

Table 2

Status Register

DESCRIPTION

The ISMS bit displays the active status of the state machine during

WRITE or BLOCK ERASE operations. The controlling logic polls this

bit to determine when the erase and write status bits are valid.

Issuing an ERASE SUSPEND places the ISM in the suspend mode

and sets this and the ISMS bit to “1.” The ESS bit will remain “1” until

an ERASE RESUME is issued.

ES is set to “1” after the maximum number of ERASE cycles is

executed by the ISM without a successful verify. ES is only cleared

by a CLEAR STATUS REGISTER command or after a RESET.

WS is set to “1” after the maximum number of WRITE cycles is

executed by the ISM without a successful verify. WS is only cleared

by a CLEAR STATUS REGISTER command or after a RESET.

VPPS detects the presence of a VPP voltage. It does not monitor VPP

continuously, nor does it indicate a valid VPP voltage. The VPP pin is

sampled for 3.3V or 5V after WRITE or ERASE CONFIRM is given. VPPS

must be cleared by CLEAR STATUS REGISTER or by a RESET.

Reserved for future use.

2Mb Smart 3 Boot Block Flash Memory

F48.p65 – Rev. 1/00

11

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2000, Micron Technology, Inc.