MT46H16M16 데이터 시트보기 (PDF) - Micron Technology

부품명

상세내역

제조사

MT46H16M16 Datasheet PDF : 79 Pages

| |||

256Mb: x16, x32 Mobile DDR SDRAM

Register Definition

CAS Latency

The CAS latency is the delay, in clock cycles, between the registration of a READ

command and the availability of the first output data. The latency can be set to two or

three clocks, as shown in Figure 7 on page 18.

For CAS latency three (CL = 3), if the READ command is registered at clock edge n, then

the data will nominally be available at (n + 2 clocks + tAC). For CL = 2, if the READ

command is registered at clock edge n, then the data will be nominally be available at (n

+ 1 clock + tAC).

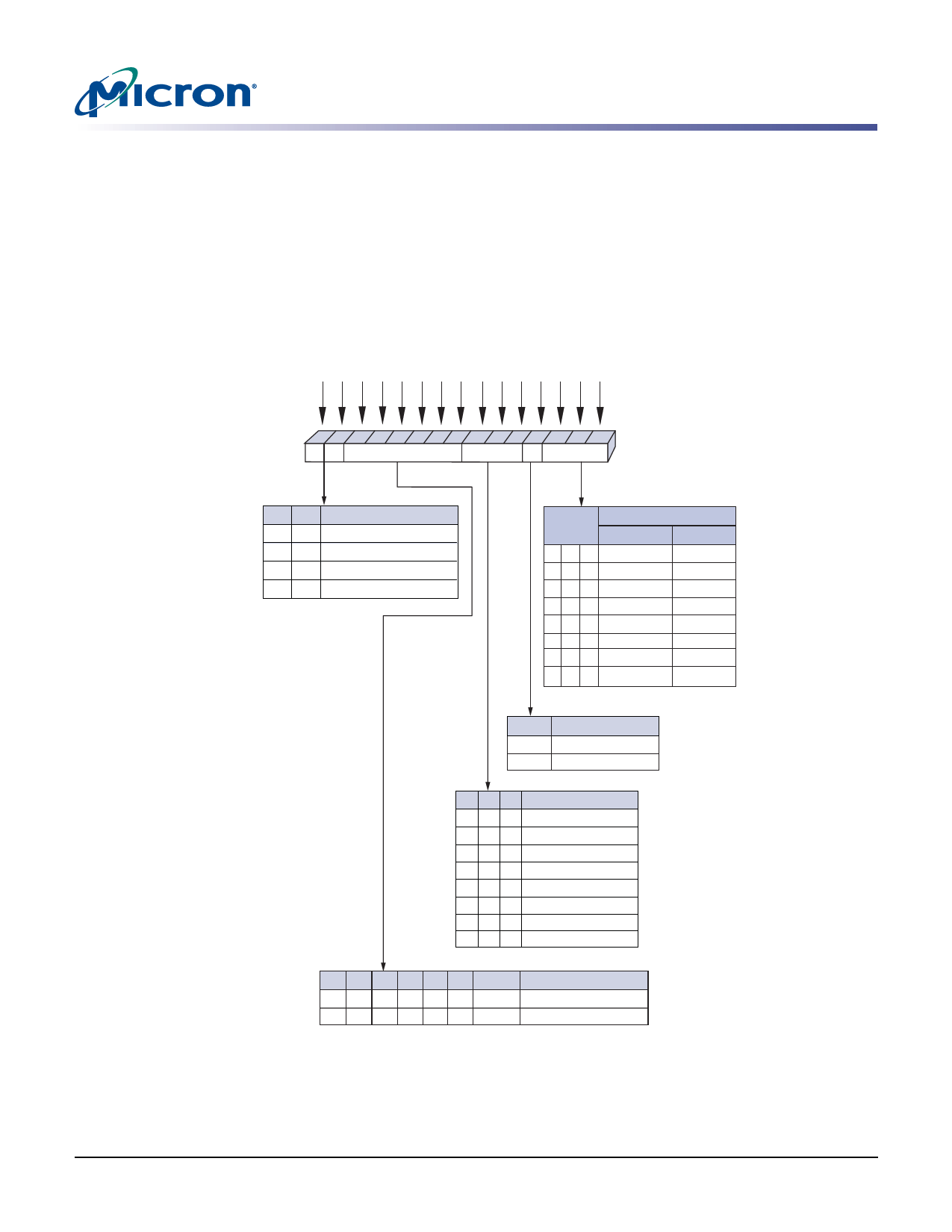

Figure 6: Standard Mode Register Definition

BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Bus

14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Standard Mode Register (Mx)

0 0 Operating Mode CAS Latency BT Burst Length

M14 M13

00

01

10

11

Mode Register Definition

Standard mode register

Reserved

Extended mode register

Reserved

M2 M1M0

0 00

0 01

0 10

0 11

1 00

1 01

1 10

1 11

Burst Length

M3 = 0

M3 = 1

Reserved

Reserved

2

2

4

4

8

8

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

M3

Burst Type

0

Sequential

1

Interleaved

M6 M5 M4

000

001

010

011

100

101

110

111

CAS Latency

Reserved

Reserved

2

3

Reserved

Reserved

Reserved

Reserved

M12 M11 M10 M9 M8 M7 M6–M0 Operating Mode

0 0 0 0 0 0 Valid Normal operation

––––– –

All other states reserved

PDF: 09005aef82091978 / Source: 09005aef8209195b

MT46H16M16LF__2.fm - Rev. H 6/08 EN

16

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2005 Micron Technology, Inc. All rights reserved.