MT46H16M16 데이터 시트보기 (PDF) - Micron Technology

부품명

상세내역

제조사

MT46H16M16 Datasheet PDF : 79 Pages

| |||

256Mb: x16, x32 Mobile DDR SDRAM

Register Definition

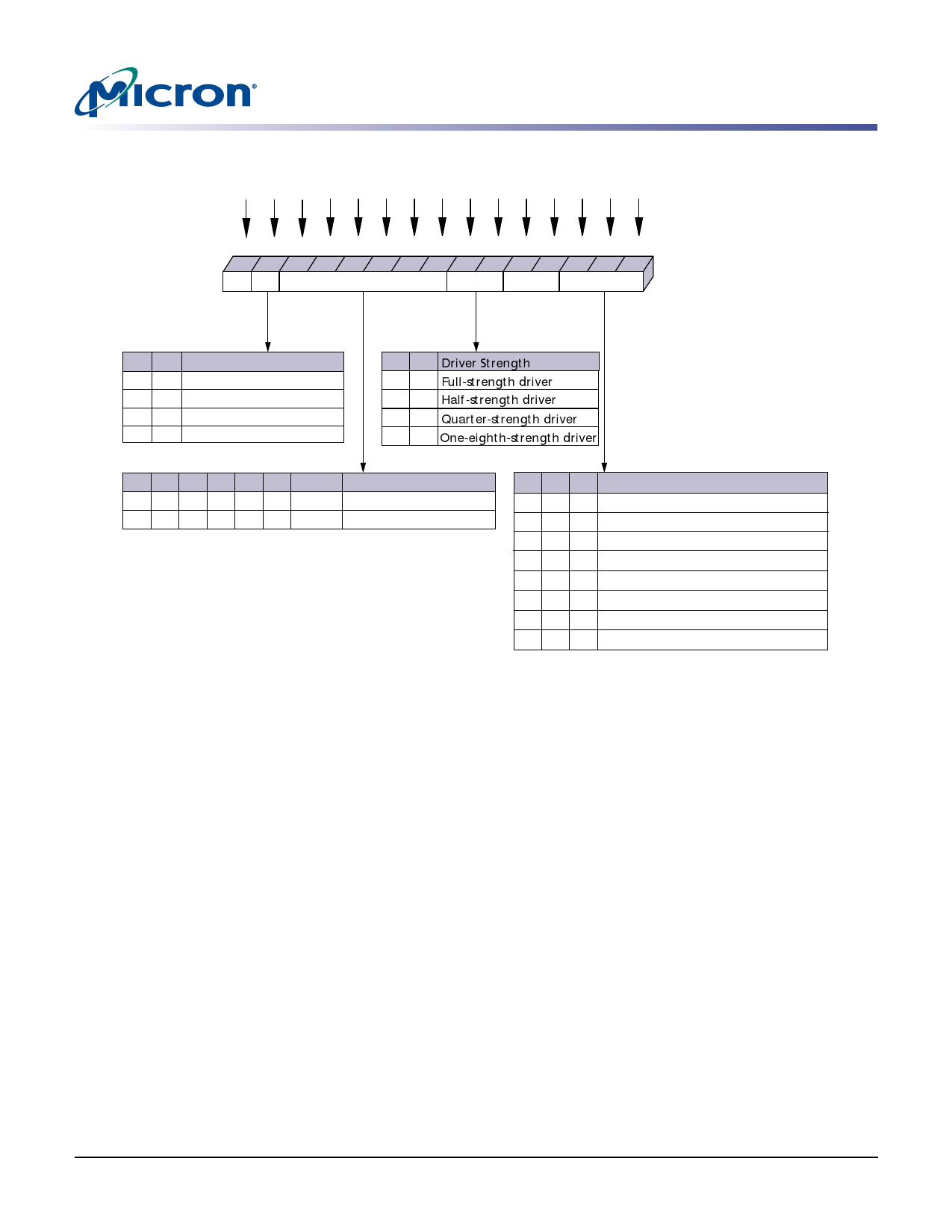

Figure 8: Extended Mode Register

BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Bus

E14 E13 E12 E11 E10 E9 E8 E7 E6 E5 E4 E3 E2 E1 E0

14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

10

Set to “0”

DS TCSR1

PASR

Extended Mode

Register

E14 E13 Mode Register Definition

0 0 Standard mode register

0 1 Reserved

1 0 Extended mode register

1 1 Reserved

E6 E5 Driver Strength

0 0 Full-strength driver

0 1 Half-strength driver

1 0 Quarter-strength driver

1 1 One-eighth-strength driver

E12 E11 E10 E9 E8 E7 E6–E0 Operating Mode

0 0 0 0 0 0 Valid Normal operation

–– – – – –

– All other states reserved

E2 E1 E0

000

001

010

011

100

101

110

111

Partial-Array Self Refresh Coverage

Full array

Half array

Quarter array

Reserved

Reserved

One-eighth array

One-sixteenth array

Reserved

Notes: 1. On-die temperature sensor is used in place of TCSR. Setting these bits will have no effect.

Stopping the External Clock

One method of controlling the power efficiency in applications is to throttle the clock

that controls the DDR SDRAM. Control the clock in two ways:

• Change the clock frequency.

• Stop the clock.

The Mobile DDR SDRAM enables the clock to change frequency during operation only if

all the timing parameters are met and all refresh requirements are satisfied.

The clock can be stopped if no DRAM operations are in progress that would be affected

by this change. Any DRAM operation already in process must be completed before

entering clock stop mode; this includes the following timings: tRCD, tRP, tRFC, tMRD,

tWR, and all data-out for READ bursts.

For example, if a WRITE or a READ is in progress, the entire data burst must be complete

prior to stopping the clock. For READs, a burst completion is defined when the read

postamble is satisfied. For WRITEs, a burst completion is defined when the write post-

amble and tWR or tWTR are satisfied.

PDF: 09005aef82091978 / Source: 09005aef8209195b

MT46H16M16LF__2.fm - Rev. H 6/08 EN

20

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2005 Micron Technology, Inc. All rights reserved.